## Simple Techniques for Isolating and Correcting Common Application Problems with UC3625 Brushless DC Motor Drives

### by Mickey McClure

The UC3625 brushless DC motor control IC incorporates many useful features which greatly simplify the design of low cost and reliable brushless DC motor drive systems. Although the controller IC is designed for ease of circuit implementation, a few precautions must be taken to insure proper operation. This design note highlights a few areas where the IC may not operate correctly if suitable design techniques are not followed.

#### REFERENCE VOLTAGE

A common application problem is inadequate decoupling and/or excessive loading on the VREF pin of the UC3625. As the data sheet indicates, the maximum recommended current drain on this node is 30mA DC. Much of the UC3625 internal logic is also referenced off of this node and any transient or noise spikes on the VREF pin can result in improper circuit operation. When the VREF pin is affected by noise, the result is usually a "lock up" condition where the motor drive outputs become disabled. This may result from a false trip of the under-voltage lock-out circuit, a false trip of soft start, or an improper decode of the Hall sensors. Other protection signals such as RC-Brake or ISENSE may be affected as well.

A simple trouble shooting technique can be used to determine when an upset of the UC3625 internal logic is causing the lock up condition. The VREF pin of the IC should be isolated from the rest of the circuit and decoupled with at least  $0.1\mu F.$  Any external +5V circuitry should be powered off of a separate bench supply. The problem should immediately go away if the VREF pin is the culprit. The motor should now operate normally, with no lock up condition.

The solution to this problem will usually involve both reducing the external current drain on VREF and increased decoupling. Every effort should be made to reduce the DC current drain as low as possible so that any AC currents will have less impact on VREF.

The Hall sensors should be powered by something other than VREF, such as VCC. While there is no general rule on how much DC current is too much, as DC currents approach 30mA, there will be more reason to suspect that VREF is the source of the lock up condition.

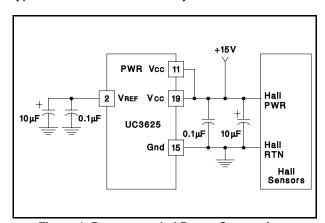

AC current will be drawn from the VREF point when it is used to provide the pull up voltage for the Hall inputs to the UC3625. Noise spikes caused by this current drain may be severe enough to latch false logic states on the internal protection circuitry if adequate decoupling is not provided. The reference voltage should always be decoupled to ground with a high quality ceramic capacitor of at least 0.1µF located as close as possible to VREF and ground pins. An electrolytic capacitor should be placed in parallel with the ceramic capacitor if there is any significant DC loading on the reference voltage. A value of 10µF is usually sufficient. The placement of the electrolytic capacitor is not as critical, but it should be located as close to the ceramic capacitor as practicality will allow. Figure 1 shows the recommended power connections and decoupling for a typical UC3625 motor drive system.

Figure 1: Recommended Power Connections and Decoupling

Design Note DN-50

#### HALL INPUTS

High power motor drive systems are frequently characterized by large noise spikes induced by high frequency switching. Under certain conditions these noise spikes can trigger Hall sensor inputs to latch improper commutation states. If an improper commutation state is latched, the correct state is then locked out for the duration of the tach-out pulse. The result is not generally a lock out condition, but rather a motor that responds in a sluggish or unpredictable manner.

As indicated by the UC3625 data sheet, any change in the H1, H2, or H3 inputs loads data from the position sensor latches. Because the position latches are inhibited for the duration of the user programmable tach-out pulse, a noise induced state will lock out the correct commutation state. The power amplifier will then energize the wrong windings of the motor, possibly resulting in reduced torque, or zero or negative torque depending on which incorrect state is latched in. The controller will allow a new state to latch once the tach-out pulse times out. Normal operation may resume at this time, or the noise related problems may continue. The response of the motor is therefore erratic and unpredictable.

This problem can be traced with a logic analyzer or four channel oscilloscope connected to the three Hall inputs and the tach-out pulse. For normal operation, the logic analyzer should display the correct sequence of the Hall signals, and the tach-out pulse should occur at regular intervals proportional to the motor velocity. Incorrect commutation states are indicated by the tach-out pulse occurring at random intervals. These incorrect states may or may not show up on the analyzer display, depending on the frequency and amplitude of the noise.

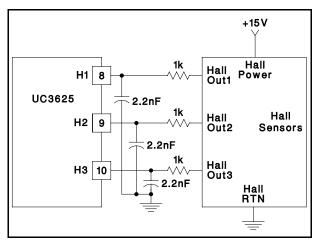

The problem can usually be corrected by passive filtering of the Hall inputs. An RC network of 1k and 2.2nF is recommended with the filter components located as close as possible to the IC. Small delays in the filter are not a problem because the sensors normally generate modified gray code with only one output changing at a time. The rise and fall times of the Hall signal edges must be shorter than 20µs for correct tachometer operation. Figure 2 depicts the recommended implementation of this filter technique.

Figure 2: Recommended Hall Filtering

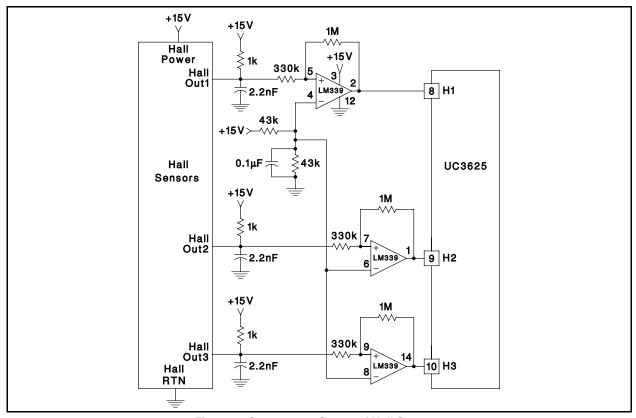

A more noise tolerant solution involves inserting comparators between the Hall sensors and the UC3625 if the passive technique is not sufficient. Because Hall sensors are typically open collector drivers, their outputs can easily become corrupted when driving long cables in a high noise environment. Much greater signal integrity can be achieved by using comparators configured with a large amount of hysteresis to attain greater noise margin. They must be configured in the noninverting mode so that the correct Hall states will be latched by the UC3625. Figure 3 shows an example circuit for driving the Hall inputs with comparators.

### **CURRENT SENSE CIRCUITRY**

The UC3625 current sense circuitry must also be configured correctly to prevent improper circuit response. Noise problems may cause the UC3625 to supply less current to the motor than the controller commands, resulting in poor motor response, and possibly undesired torque limiting.

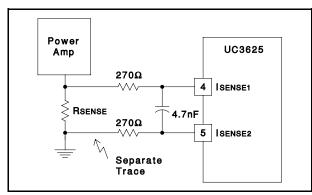

The most important factor in achieving proper current limit response is a correct differential measurement of the voltage across the current sense resistor. Separate traces must be run from the ISENSE1 and ISENSE2 inputs directly to the current sense resistor. If an input filter is used, it should be balanced, and the filter resistors should tie directly to the current sense resistor. Recommended component values for the differential filter are  $270\,\Omega$  and 4.7nF. **Never** should one ISENSE input line be simply grounded and the other input driven single

Design Note DN-50

Figure 3: Comparator Sense of Hall Sensors

ended. The recommended circuit layout for the IS-ENSE1 and ISENSE2 input signals is shown in Figure 4.

Figure 4: Proper Current Sense Layout

Additional noise immunity can be achieved by adding a capacitor from the ISENSE output to ground. This capacitor should be located as close as possi-

ble to the ISENSE pin, and a low impedance path to ground for its low side is essential. Filtering at this point has the advantage of allowing fast signal inversions to be correctly processed by the absolute value circuit before filtering takes place.

If high levels of common mode noise or ground bounce are affecting the ISENSE inputs it may be necessary to decouple the ISENSE inputs (pins 4 and 5) to ground with 470pF capacitors. These capacitors will shunt out any high frequency common mode noise, and allow for a more accurate measurement of true motor current.

# NONLINEARITY PROBLEMS ASSOCIATED WITH NOISE ON THE TIMING CAPACITOR

Switching noise can result in discontinuities in the linear response of the PWM circuitry if the timing capacitor on the RC-OSC pin is not located properly. The UC3625 creates the sawtooth waveform by measuring the voltage across the capacitor tied be-

Design Note DN-50

tween RC-OSC and ground. This voltage is charged by a constant current source, and is discharged when a fixed threshold is reached. The output duty cycle of the power stage is determined by comparing the error amplifier output to the sawtooth waveform. When the magnitude of the sawtooth waveform is greater than the output of the error amplifier, the output stage is switched off.

Large current spikes can result in localized ground bounce when the power stage switches. The low side of the capacitor can be "pumped up" if the timing capacitor is not located near the IC. This problem will result in the oscillator comparator tripping early, and the sawtooth waveform will jump to a higher frequency. The effect will be a nonlinear PWM gain function. Since the PWM is usually part of the forward loop, this will not be a problem in many closed loop systems because the outer control loop will simply compensate for the nonlinearity.

For cases where the nonlinearity is a problem, the situation can usually be mitigated by connecting the timing capacitor directly across the RC-OSC and GND pins of the UC3625. Since the internal compa-

rator is referenced from this local ground point, the correct trip point will be maintained and the frequency of the oscillator will remain constant.

For some cases it may be necessary to add a low value resistor in series with the Pwr-Vcc pin or the output (PD and PU) pins of the UC3625. These resistors will limit the peak value of transient currents in the output driver stage of the IC. By minimizing these currents, the amount of ground bounce can be reduced, and therefore the nonlinearity problem can be curtailed.

While the previously described techniques will result in a more robust and reliable motor drive design, they are by no means the answer to every problem. As with all analog circuitry, there is no substitute for good circuit design and layout practice when designing with the UC3625. Every effort should be made to keep all signal runs as short as possible, and avoid running sensitive traces near each other. Finally, proper grounding techniques should always be maintained, as well as careful attention to EMI reduction.