# **Ethernet Coaxial Impedance Monitor**

#### FEATURES

- Compatible with IEEE 802.3 10Base5, 10Base2, and 10BaseT

- Preset and Adjustable Data Thresholds

- Protects DTE from Spurious

Data

- Prevents Erroneous

Transmission Through

Repeaters

- Detects Cable Termination Errors

- Detects Cable Impedance Errors

### DESCRIPTION

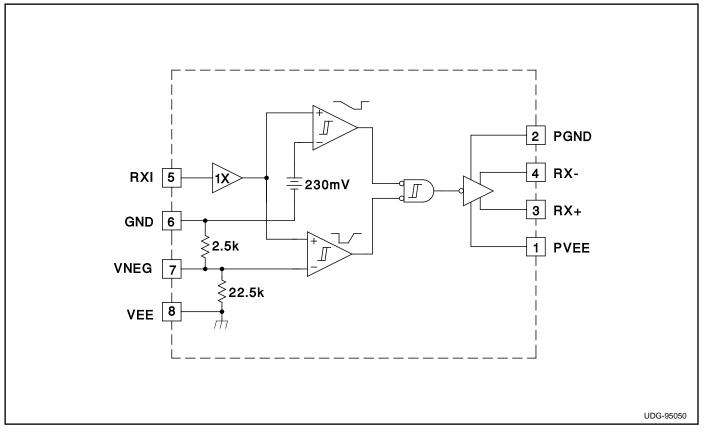

The UC5661 is a monolithic integrated circuit which functions as an Ethernet Coaxial Impedance Monitor (CIM). This IC is intended to augment the receive (RX) function of IEEE 802.3 Coaxial Transceiver Interface (CTI) circuits. The UC5661 implements a hardware algorithm to detect reflections on the Ethernet coaxial cable or twisted pair which are caused by improper network termination or physical medium damage. If a physical problem is detected, the UC5661, whose receiver outputs operate in parallel with the CTI, immediately squelches the receive data, preventing the propagation of invalid network packets. During ordinary operation, the CIM RX outputs enable at the beginning of the data packet preamble, making it transparent to normal CTI functions. The valid data threshold, although preset for thick and thin-wire Ethernets, may be adjusted with the addition of one or two external resistors to meet 10BaseT requirements.

A secondary system design feature is provided by the UC5661. At the completion of a normal data transmission, the CIM Squelch activates much faster than typical transceiver ICs. The receiver outputs of the UC5661 have been designed to properly terminate the data packet, even with RX data transformers as small as 16 $\mu$ H, possibly allowing for smaller and less expensive system implementations. In these cases, end-of-packet squelch overshoot will be held to less than 100mV.

#### BLOCK DIAGRAM

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (PVEE,VEE)                                               |

|-------------------------------------------------------------------------|

| Input Voltage (RXI)+2V to -10V                                          |

| Operating Temperature Range                                             |

| Junction Temperature (Note 1)+125°C                                     |

| Storage Temperature Range55°C to +150°C                                 |

| Lead Temperature (Soldering, 10 sec.)+300°C                             |

| All currents are positive into, negative out of the specified terminal. |

| Consult Packaging Section of Databook for thermal limitations           |

| and considerations of packages.                                         |

| Note 1: The devices are guaranteed by design to be                      |

Det 1: The devices are guaranteed by design to be functional up to the absolute maximum junction temperature.

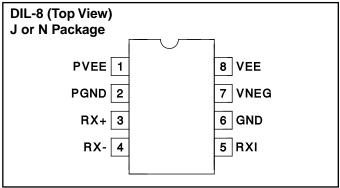

## **CONNECTION DIAGRAMS**

**DC ELECTRICAL CHARACTERISTICS** Unless otherwise stated, these specifications apply for  $T_A = 0^{\circ}C$  to 70°C, VEE = PVEE = -9.0V, and RL = 500 ohms,  $T_A = T_J$ .

| PARAMETER                        | TEST CONDITIONS                      | MIN   | TYP  | MAX  | UNIT |

|----------------------------------|--------------------------------------|-------|------|------|------|

| Supply Current                   | Outputs Locked or Unlocked, Unloaded |       | 10   | 20   | mA   |

| Input Bias Current               | RXI = 0V                             |       | 2    | 5    | μA   |

| Input Shunt Resistance           | RXI = -2V  to  0V                    | 0.200 | 45   |      | MΩ   |

| Input Shunt Capacitance          | (Note 1)                             |       | 3    | 4    | pF   |

| VNEG (Valid Data Reference)      | VNEG = open                          | -980  | -900 | -830 | mV   |

| RX Output Voltage High (Squelch) |                                      | -1.2  | -0.9 | 0    | V    |

| RX Output Voltage Low (Enable)   |                                      | -6    | -3.7 | -3.2 | V    |

| Output Short Circuit             | RX+=RX-=9V                           | -150  |      |      | mA   |

| Valid Data Threshold             |                                      | -980  | -900 | -830 | mV   |

| Data Reflection Threshold        |                                      | 200   | 230  | 300  | mV   |

Note 1: Guaranteed by design. Not 100% tested in production.

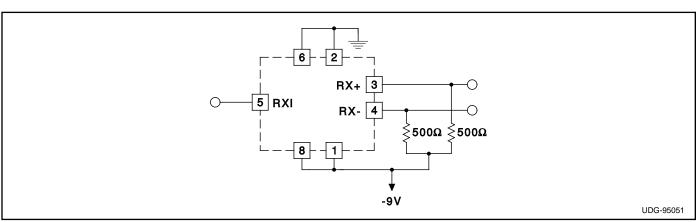

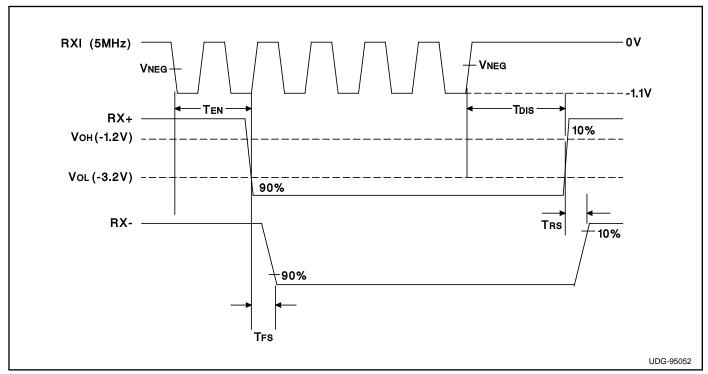

**AC ELECTRICAL CHARACTERISTICS** Unless otherwise stated, these specifications apply for  $T_A = 0^{\circ}C$  to 70°C, VEE = PVEE = -9.0V, and RL = 500 ohms,  $T_A = T_J$ .

| PARAMETER                        | TEST CONDITIONS  | MIN | TYP  | MAX  | UNIT |

|----------------------------------|------------------|-----|------|------|------|

| TEN RX Enable Delay              | See Figures 1, 2 |     | 100  | 400  | ns   |

| TDIS RX Disable Delay            | See Figures 1, 2 | 250 | 340  | 475  | ns   |

| TFS RX+ to RX– Falling Edge Skew | See Figures 1, 2 |     | 5    | 20   | ns   |

| TFR RX+ to RX– Rising Edge Skew  | See Figures 1, 2 |     | 5    | 20   | ns   |

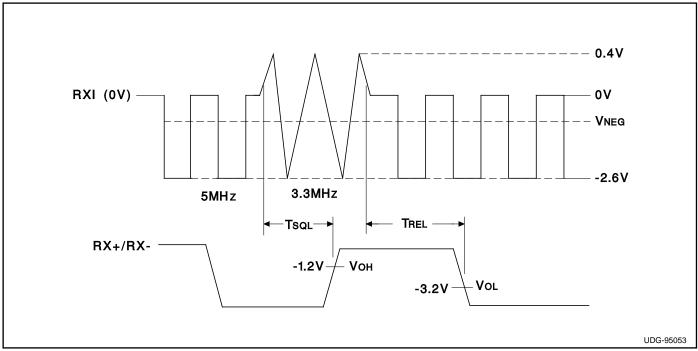

| TsoL RX Squelch Delay            | See Figures 1, 3 |     | 230  | 2000 | ns   |

| TREL RX Release Delay            | See Figures 1, 3 | 500 | 1150 | 1500 | ns   |

Figure 1. Switching Test Circuit

Figure 2. Input/Output Timing Diagram

Figure 3. Short Detect Timing Diagram

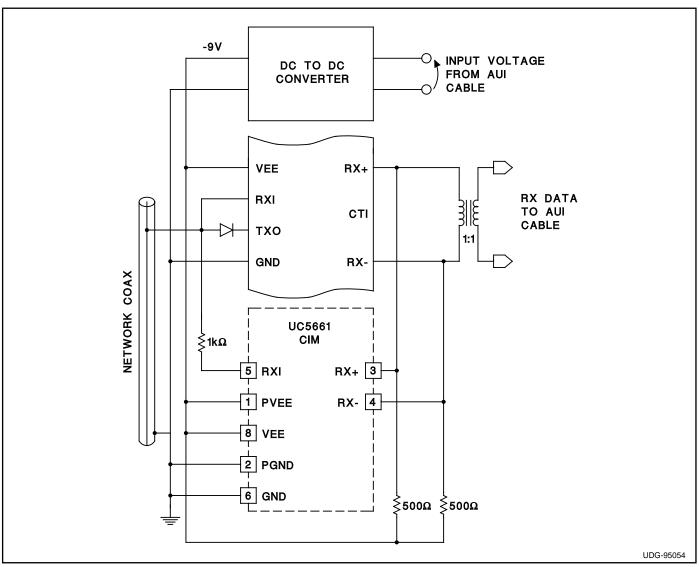

**Figure 4. Typical Application**

Figure 4 shows the UC5661 (SDI) being used with a Coaxial Transceiver Interface (CTI) device. The primary function of the SDI is to detect LAN cable shorts (or other impedance matching problems) and appropriately squelch the RX outputs of the CTI device to prevent the transmission of corrupted network data. The secondary function of the SDI is to provide improved RX squelching at the completion of a normal data transmission.

To perform the two functions, SDI uses two threshold voltages, Data Reflection Threshold (DRT), and the Valid

Data Threshold (VDT). During transmission SDI looks for signal activity above ground and below ground. In the event that the magnitude of the input voltage exceeds DRT the outputs will be locked within  $2\mu$ s and will remain locked for 0.5 to 1.5 $\mu$ s after the last edge below DRT (see Figure 3). During signal activity below ground when the signal goes below VDT the outputs will unlock within 400ns. While unlocked, if the input exceeds VDT the outputs will lock within 250 to 475ns relative to the last positive going edge (Figure 2).