# PRELIMINARY Buck Pulse Width Modulator Stepdown Voltage Regulator

## FEATURES

- Provides Simple Single Inductor Buck PWM Step-Down Voltage Regulation

- Drives External High Side

NMOS Switch

- 14V to 72V Input Voltage Operating Range

- Contains 100kHz Internal Oscillator, 2V Reference and UVLO

- Includes Soft Start on Power

Up

- Includes Overcurrent Shutdown Followed by Soft Start

## DESCRIPTION

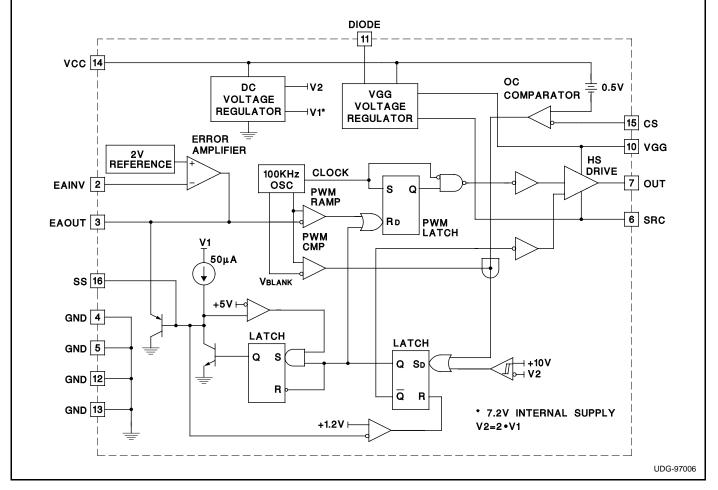

The UC3578 is a high side buck pulse width modulator with a floating gate driver which steps down and regulates a positive input voltage. The chip is optimized for use in a single inductor buck switching converter employing an external NMOS switch. The block diagram consists of a precision reference, an error amplifier configured for voltage mode operation, a 100kHz oscillator, a PWM comparator with latching logic and a high current gate driver. The UC3578 includes an under voltage lockout circuit to insure sufficient input supply voltage is present before any switching activity can occur, and overcurrent shutdown followed by soft start. Input current can be sensed and limited to a user defined maximum.

## BLOCK DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

| VCC                                                                 |

|---------------------------------------------------------------------|

| EAINV                                                               |

| EAOUT                                                               |

| SS –0.3V to +10V                                                    |

| DIODE                                                               |

| VGG                                                                 |

| CS VCC – 5V to VCC + 0.6V                                           |

| IOUT Pulsed                                                         |

| SRC –0.6V to VCC                                                    |

| Storage Temperature                                                 |

| Junction Temperature                                                |

| Lead Temperature (Soldering, 10 sec.) +300°C                        |

| Currents are positive into, negative out of the specified terminal. |

| Consult Packaging Section of Databook for thermal limitations       |

| and considerations of packages.                                     |

|                                                                     |

# **CONNECTION DIAGRAM**

| DIL-16.SOIC-16(Top View)<br>N or DP Packages |  |          |  |  |  |  |

|----------------------------------------------|--|----------|--|--|--|--|

|                                              |  |          |  |  |  |  |

| N/C 1                                        |  | 16 SS    |  |  |  |  |

| EAINV 2                                      |  | 15 CS    |  |  |  |  |

| EAOUT 3                                      |  | 14 VCC   |  |  |  |  |

| GND 4                                        |  | 13 GND   |  |  |  |  |

| GND 5                                        |  | 12 GND   |  |  |  |  |

| SRC 6                                        |  | 11 DIODE |  |  |  |  |

| OUT 7                                        |  | 10 VGG   |  |  |  |  |

| N/C 8                                        |  | 9 N/C    |  |  |  |  |

|                                              |  |          |  |  |  |  |

**ELECTRICAL CHARACTERISTICS** Unless otherwise specified,  $-40^{\circ}$ C to  $85^{\circ}$ C for the UC2578, and  $0^{\circ}$ C to  $70^{\circ}$ C for the UC3578, VCC = 14V, VGG = 14V, TA = TJ.

| PARAMETER                        | PARAMETER TEST CONDITIONS                 |      | TYP | MAX  | UNITS |

|----------------------------------|-------------------------------------------|------|-----|------|-------|

| Oscillator Section               |                                           |      |     |      |       |

| Frequency                        | VCC = 14V to 72V, EAINV = 1.9V, TJ = 25°C | 100  | 110 | 120  | kHz   |

|                                  | VCC = 14V to 11V, Over Temperature        | 90   |     | 120  | kHz   |

| Error Amplifier Section          |                                           |      |     |      |       |

| EAINV                            | EAOUT = EAINV                             | 1.97 | 2   | 2.03 | V     |

| IEAINV                           | EAOUT = EAINV                             |      | 100 | 300  | nA    |

| EAVOL                            | EAOUT/EAINV, 25°C                         | 70   | 80  |      | dB    |

| EAOUT High                       | EAINV = 1.9V, IEAOUT = $-100\mu$ A        | 5.5  | 6.2 |      | V     |

| EAOUT Low                        | EAINV = 2.1V, ΙΕΑΟυΤ = 100μΑ              |      | 0.8 | 1    | V     |

| Unity Gain Bandwidth             | TJ = 25°C, F = 100kHz                     | 0.85 | 1   | 1.15 | MHz   |

| PSRR, EAOUT                      | EAOUT = EAINV, VCC = 14V                  | 80   | 90  |      | dB    |

| Current Sense Comparator Section |                                           |      |     |      |       |

| Threshold (Referred to VCC)      |                                           | 0.4  | 0.5 | 0.6  | V     |

| Input Bias Current               | CS = VCC - 0.4V                           |      | 0.2 | 1    | μA    |

| Propagation Delay                | VOVERDRIVE = 250mV                        |      | 0.7 | 1    | μs    |

| Blanking Time                    | VOVERDRIVE = 250mV                        | 0.8  | 1.5 | 2.5  | μs    |

| Gate Drive Output Section        |                                           |      |     |      |       |

| VOH                              | IOUT = -200mA                             | 10   | 11  |      | V     |

| VOL                              | IOUT = 20mA                               | 0.2  |     | 0.36 | V     |

|                                  | IOUT = 200mA                              |      | 1.5 | 2    | V     |

| Rise Time                        | $T_J = 25^{\circ}C, C_{LOAD} = 1nF$       |      | 40  | 70   | ns    |

| Fall Time                        | $T_J = 25^{\circ}C, C_{LOAD} = 1nF$       |      | 40  | 70   | ns    |

| Pulse Width Modulator Section    |                                           |      |     |      |       |

| Maximum Duty Cycle               | EAINV = 1.9V                              | 85   | 90  |      | %     |

| Minimum Duty Cycle               | EAINV = 2.1V                              |      | 0   |      | %     |

| Modulator Gain                   | EAOUT = 2.5V to 3.5V                      |      | 30  |      | %/V   |

| Undervoltage Lockout Section     |                                           |      |     |      |       |

| Start Threshold                  | OUT – SRC, EAINV = 1.9V, SRC = 0V         | 10   | 11  | 12   | V     |

| UVLO Hysteresis                  |                                           | 1.5  | 2   | 2.5  | V     |

**ELECTRICAL CHARACTERISTICS (cont.)** Unless otherwise specified, -40°C to 85°C for the UC2578, and 0°C to 70°C for the UC3578, VCC = 14V, VGG = 14V, TA = TJ.

| PARAMETER               | TEST CONDITIONS                       | MIN  | TYP   | MAX  | UNITS |

|-------------------------|---------------------------------------|------|-------|------|-------|

| VGG Regulator Section   |                                       |      |       |      |       |

| VGG – SRC               | VCC = 72V                             | 14.5 | 15.25 | 16   | V     |

|                         | VCC = 50V, $SRC = 0V$ , $IVGG = -7mA$ | 14   | 14.75 | 15.5 | V     |

|                         | VCC = 15V, $SRC = 0V$ , $IVGG = -7mA$ | 13   | 13.75 | 14.5 | V     |

|                         | VCC = 11V, SRC = 0V, Ivgg = -7mA      | 9.5  | 10    | 10.5 | V     |

| Soft Start Ramp Section |                                       |      |       |      |       |

| Soft Start Ramp Current |                                       | -30  | -45   |      | μΑ    |

| Supply Current Section  |                                       |      |       |      |       |

| Ivcc                    | EAINV = $2.1V$ , SRC = $0V$           |      | 10    | 14   | mA    |

| Ivgg                    | EAINV = 2.1V, SRC = 0V                |      | 7     | 10.5 | mA    |

## **PIN DESCRIPTIONS**

**CS:** Peak current limit sense pin. Senses the current across a current sense resistor placed between VCC and the drain of the NMOS buck switch. OUT will be held low (NMOS buck switch off) if VCC – CS exceeds 0.5V.

**DIODE:** An external small signal diode (1N4148 typical) is connected here, anode to VCC and cathode to DIODE, to implement the VGG regulator function.

**EAINV:** Inverting input to error amplifier. VOUT sense feedback is connected to this pin. The non-inverting input of the error amplifier is internally connected to 2V.

**EAOUT:** Output of the error amplifier. Use EAOUT and EAINV for loop compensation components.

GND: Circuit Ground.

**OUT:** Gate drive for the external NMOS switch connected between VCC and the buck inductor.

## **APPLICATION INFORMATION**

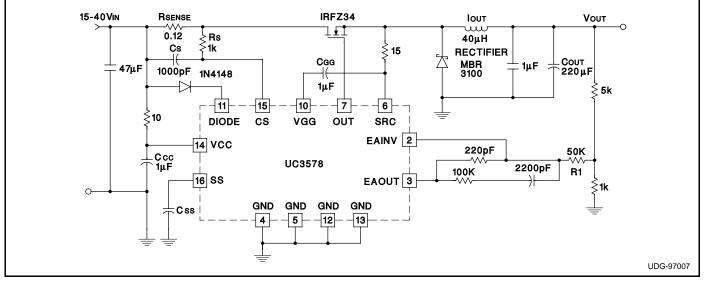

The UC3578 Floating Buck Controller is a high frequency switching regulator with a floating driver which provides PWM control for non-isolated buck converters. The controller operates at a fixed 100 kHz switching frequency, and in voltage mode control. The duty cycle range of the PWM output is 0% to 90% allowing for a wide range of input voltages (14V minimum with transients to 72V). The regulator features an undervoltage lockout threshold of 11V with approximately 2V hysterisis as well as soft start capability. A typical application circuit is shown in Figure 2 for a 15V to 40V input and a 12V at 3A output.

As shown in Figure 2 for proper operation of the floating driver an external capacitor (1 $\mu$ F ceramic) must be connected from VGG to SRC the source of the external MOSFET. This capacitor provides the energy for the high side driver. The gate drive voltage to the MOSFET is internally regulated to 14V. A diode (1N4148) is re-

**SRC:** This pin is connected to the junction of the external NMOS switch source, the floating voltage source capacitor, the free-wheeling diode cathode, and buck inductor.

**SS:** The external soft start capacitor is connected to this pin.

**VGG:** An external capacitor connected from VGG to SRC completes the floating voltage source for the floating gate driver. A  $1\mu$ F capacitor is recommended.

**VCC:** Input supply voltage. This pin supplies an internal ground referenced voltage regulator that supplies the IC and an on-chip regulated floating voltage source (VGG – SRC) used by the floating driver to drive the external NMOS buck switch. This pin should be bypassed with a high quality ceramic capacitor.

quired from the input voltage to DIODE. This allows the floating drive capacitor to charge during conduction of the output rectifier but prevents its discharge back into the supply rail. A 1 $\mu$ F ceramic capacitor is recommended from VCC to ground to provide high frequency decoupling. Additional decoupling of this pin could be accomplished by a low value resistor between VCC and VIN and a 1 $\mu$ F capacitor from VCC to GND as shown in the schematic.

#### **CURRENT LIMIT**

The current sense pin provides overcurrent shutdown. As can be seen from the block diagram, the overcurrent comparator is wire ANDed with the oscillator after an internally set blanking time. The ILIMIT threshold level is set by the current sense resistor from RSENSE.

$$I_{\text{LIMIT}} = \frac{0.5\text{V}}{\text{RSENSE}}$$

## **APPLICATION INFORMATION (cont.)**

## **Figure 2. Typical Application**

An optional filter can be added (RsCs) from the current sense resistor to CS to provide high frequency filtering of the current sense signal if necessary.

During a current limit condition, the soft start capacitor on SS is discharged until its voltage level reaches 1.2V. During this time, a duty cycle clamp is activated to approximately 0.6V above the voltage level on the SS capacitor. This condition persist until the SS capacitor is discharged to 1.2V, thus disabling the output driver. At this time, the SS capacitor is allowed to charge to 5V through the 50 $\mu$ A current source and normal operation resumes when the SS capacitor reaches 5V. During the condition described, the regulator enters a hiccup current limit mode of operation which limits the power dissipation in the MOSFET and output rectifier under a short circuit condition.

## ERROR AMPLIFIER

The onboard error amplifier of the UC3578 is a voltage amplifier with its non-inverting input tied to an internal 2V reference. As usual, loop compensation can be added from the inverting input of EAINV to the error amplifier output at EAOUT. Consideration must be given when choosing the values of the compensation components around the amplifier so that the output swing of the amplifier is not restricted. The output of the amplifier can source  $100\mu$ A typically.

#### GENERAL

As in any buck converter, when the switch is off, the MOSFET's source flies low due to the conduction of the free-wheeling rectifier. The source (SRC) is pulled below ground by an amount determined by the forward voltage

drop of the rectifier and by any transient voltage spike from inductance in this path. The occurrence of this condition could result in erratic operation of the IC during this period if the negative excursion is not limited. This is because of conduction of current in the substrate of the IC due to the source pin being pulled below ground and forward biasing the internal substrate PN junction. To limit this effect, a small resistor ( $15\Omega$ ) can be placed in series between the MOSFET source and the SRC pin as shown in Figure 2. Too large a resistor will limit the drive to the MOSFET and result in startup problems with the regulator. A Schottky rectifier is used for the free-wheeling diode to limit the negative excursion of the source. This will also limit the reverse recovery current thus limiting the inductive voltage spike.

In applications where transient load excursions may result in a no load condition, it is necessary that the output of the regulator be loaded with a small load current (10mA to 15mA). This will prevent the output voltage from going unregulated at no load. This small load current is necessary for proper operation of the floating driver since the source must fly low to charge up the floating driver capacitance.

## THERMAL CONSIDERATIONS

For proper operation and reliability of the UC3578, proper thermal management is essential. It is important that the designer keep in mind that with surface mount packages, a significant amount of their heat that the device generates is conducted out through the lead frame. Because of this, the PCB design becomes a critical part of the thermal management system. Worst case junction-to-ambient thermal resistance for different package

## **APPLICATION INFORMATION (cont.)**

configurations are given in a table in the data book in the package information section.

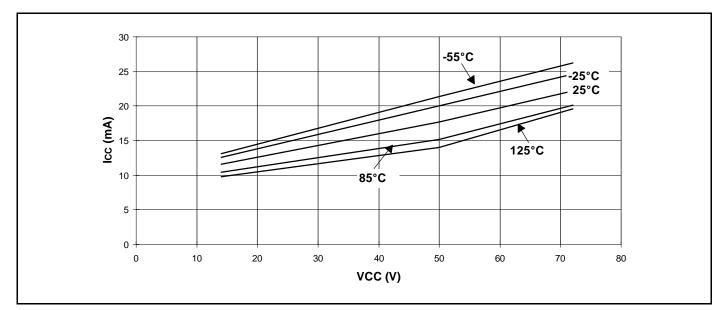

The maximum ambient operating temperature is an important factor in determining what the maximum operating voltage can be for a particular application. For example, if we assume a maximum operating ambient temperature of 70°C we can determine what the maximum allowable input voltage can be given other parameters such as package thermal impedance and MOSFET total gate charge by following the procedure outlined below;

$T_{JMAX} - T_{A} = 125^{\circ}C - 70^{\circ}C = 55^{\circ}C$ (1)

$$Pd = \frac{55^{\circ}C}{58^{\circ}C/W} = 0.95W$$

(2)

where 58°C/W is the worst case theta j-a for the 16 pin DP package and Pd is the package power dissipation.

$$Pd = (Qg \times 100 \text{kHz} + 19 \text{mA}) \bullet \text{Vin}$$

(3)

where Qg is the total MOSFET gate charge and 19mA is the maximum quiescent current for the UC3578 (Icc + IGG) from the data sheet. The switching frequency of the buck converter is 100kHz.

The gate charge can be determined from the MOSFETdata sheet. As an example, for a IRFZ34 which has a total gate charge of 46nC, substituting for Pd in equation 3: 0.95W = (46nC x 100 kHz + 19mA) VIN

$$V_{\text{IN MAX}} = \frac{0.95W}{0.0236A} = 40V$$

Therefore, at 70°C using a IRFZ34 MOSFET the maximum input voltage is limited to 40V to maintain a maximum junction temperature of 125°C in the 16 pin DP package.

Higher input voltages can be achieved by choosing a MOSFET with a lower total gate charge or by a reduced ambient operating temperature or by reducing the theta j-a of the package by improving the PCB mounting method. It is recommended that the four GND pins (4,5,12 and 13) be connected to a ground plane to provide a low resistance thermal path. If a ground plane is not available, a heat spreader on a double sided PC board is recommended.

Note: Thermal impedance number is based on device mounted to 5 square inch FR4 PC board with one ounce copper. From Unitrode 95-96 data book Table 1, page 9-8, when resistance range is given, lower thermal impedance values are for 5 square inch aluminum PC board.

Figure 3. ICC vs. VCC vs. Temperature

UNITRODE CORPORATION 7 CONTINENTAL BLVD. • MERRIMACK, NH 03054 TEL. (603) 424-2410 • FAX (603) 424-3460