# 12V Boost Regulator

## **FEATURES**

- 3V to 5V Input Voltage Range

- Peak Current Limited PWM Control

- 250µA Operating Supply Current

- 25µA Shutdown Supply Current

- 12V/100mA Output

- Available in 8 Pin DIL and SOIC Packages

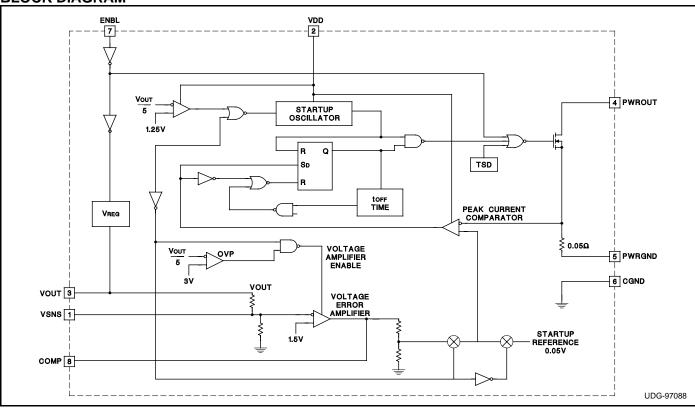

## **BLOCK DIAGRAM**

# ADVANCED INFORMATION

UCC1812 UCC2812

**UCC3812**

### DESCRIPTION

The UCC3812 is a low power boost regulator that takes a 3V to 5V input and outputs a regulated 12V at 100mA. The part uses peak current sensing with a fixed 1 $\mu$ s off time for the current control. An internal power FET with an RDSON of 200m $\Omega$  allows peak input currents up to 1A.

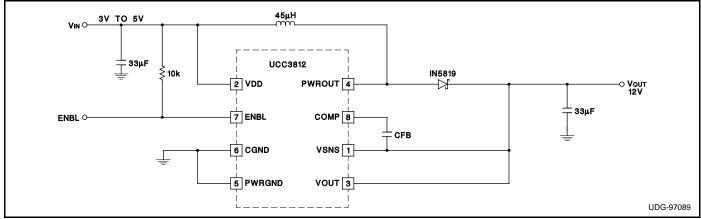

## **TYPICAL APPLICATION CIRCUIT**

## UCC1812 UCC2812 UCC3812

## **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage 6.5V                                                  |

|---------------------------------------------------------------------|

| Power Dissapation 0.4W                                              |

| Storage Temperature                                                 |

| Junction Temperature                                                |

| Lead Temperature (Soldering, 10 sec.) +300°C                        |

| Currents are positive into, negative out of the specified terminal. |

| Consult Packaging Section of Databook for thermal limitations       |

| and considerations of packages.                                     |

#### THERMAL DATA

8 Pin SOIC (D)

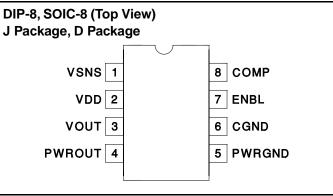

## CONNECTION DIAGRAM

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated,  $TA = 0^{\circ}C$  to 70°C for the UCC3812, -40°C to 85°C for the UCC2812, and -55°C to 125°C for the 1812. TA = TJ.

| PARAMETER                     | TEST CONDITIONS         | MIN   | TYP | MAX   | UNITS |

|-------------------------------|-------------------------|-------|-----|-------|-------|

| Overall                       |                         |       |     |       |       |

| Output Voltage                | VDD = 3V to 5V          | 11.64 | 12  | 12.36 | V     |

| Output Current                |                         |       |     | 100   | mA    |

| Minimum Startup Voltage       |                         |       |     | 3     | V     |

| Minimum Operating Voltage     |                         |       | 2.8 |       | V     |

| Load Regulation               |                         |       |     |       | mV    |

| Total Variation               |                         | 11.4  | 12  | 12.6  | V     |

| Supply Current                | ENBL = VDD, fs = 200kHz |       | 250 |       | μA    |

| Shutdown Current              | ENBL = 0V               |       | 25  |       | μA    |

| Voltage Error Amplifier       |                         |       |     |       |       |

| VOUT High                     |                         |       | 3   |       | V     |

| VOUT Low                      |                         |       | 0.1 |       | V     |

| Open Loop Gain                |                         |       | 80  |       | dB    |

| Input Bias Current            |                         |       | -50 |       | nA    |

| Input Voltage                 |                         |       | 1.5 |       | V     |

| Gain Bandwidth Product        | FIN = 100kHz, 10mVp-p   |       | 5   |       | MHz   |

| Total Variation               |                         | 11.4  | 12  | 12.6  | V     |

| Current Sense Section         |                         |       |     |       |       |

| Peak Current Sensing Accuracy | IPEAK = 1A              |       |     | 20    | %     |

| Peak Current Delay            |                         |       | 150 |       | nS    |

| Gate Driver                   |                         |       |     |       |       |

| Pull Down Resistance          |                         |       | 0.2 | 0.35  | Ω     |

| Thermal Shutdown              |                         |       |     |       |       |

| Shutdown Temperature          |                         | 155   | 165 | 175   | °C    |

| Hysteresis                    |                         |       | 10  |       | °C    |

#### **PIN DESCRIPTION**

**CGND:** Low power ground for reference and other part functions.

**COMP:** Output of the voltage error amplifier.

**ENBL:** A logic level input used to switch the device in and out of the low current shutdown mode. Pulling ENBL low puts the part in shutdown mode.

**PWRGND:** Power ground for high current DMOS output section.

PWROUT: Drain of an internal DMOS device with its

#### **APPLICATION INFORMATION**

The UCC3812 is a boost controller IC with an integrated MOSFET. The control is provided by a constant off time current loop with an outer voltage loop for output voltage regulation. The advantage of the constant off time current loop is that it provides cycle by cycle current limiting and all the benefits of current mode control such as easy compensation of the voltage loop, while being inherently stable and therefore not requiring ramp compensation. The UCC3812 takes an input voltage in the range of 3V to 5V and boosts it up to a regulated 12V output. With the MOSFET and current sensing circuitry internal to the IC, the design of the converter is very straight forward. For a maximum load current of 100mA and minimum input voltage of 3V the average input current will be 400mA. The inductor current ripple ( $\Delta I$ ) can be chosen to be half IIN. Therefore, the inductor required is:

$$L \approx \frac{V \text{IN MIN} \bullet \text{TON MAX}}{\Delta I}$$

For VIN = 3V, ton MIN =  $3\mu$ S. Therefore, the inductance required is  $45\mu$ H.

The output capacitor is chosen for ripple voltage and it's

source connected through a sense resistor to PWRGND. This device has a peak current limit of 1A.

**VDD:** The power supply input connection for the device connected to a voltage of 3V to 5V.

**VOUT:** Voltage feedback from the regulated 12V to the non-inverting input of the voltage error amplifier. This input is also used to bootstrap the gate drive to the power DMOS device.

VSNS: The inverting input to the voltage amplifier.

allowable ripple current. In general a low ESR capacitor is suggested to limit the ripple voltage. In this application an ESR of approximately  $200m\Omega$  will limit the ripple voltage (neglecting capacitive discharge) to 100mV. Several capacitors are appropriate here, a  $33\mu$ F OsCON or a  $220\mu$ F, low ESR electrolytic capacitor would be acceptable.

The diode is chosen to handle the load current. A schottky rectifier is a good choice for its low voltage drop. A 1N5819, or equivalent is appropriate here.

#### Compensation

Compensation of the converter can be accomplished with simple dominate pole compensation. For the case where  $33\mu$ F output capacitor is used, a 680pF capacitor in the feedback loop will give a 600Hz cross over frequency with a phase margin of 50°C (if the 220 $\mu$ F capacitor is used a 6.8nF feedback capacitor will result in a cross over frequency of 60Hz and phase margin of about 60°C). If higher bandwidth is required or faster transient response, a zero-pole pair can be used for compensation.