# High Bandwidth, Bidirectional 65 V Difference Amplifier

AD8216

#### **FEATURES**

±4000 V HBM ESD

Ideal for current shunt applications High common-mode voltage range

- -4 V to +65 V operating

- -40 V to +80 V survival

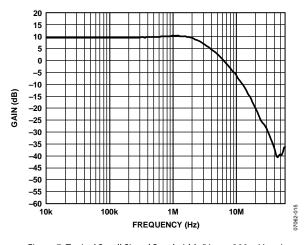

- 3 MHz bandwidth

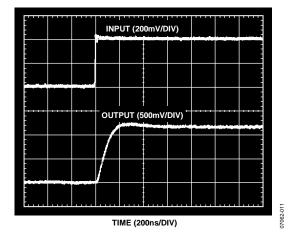

- <100 ns output propagation delay

Gain: 3 V/V

Wide operating temperature range

Die: -40°C to +150°C

8-lead SOIC: -40°C to +125°C

Adjustable output offset

**Available in 8-lead SOIC**

**Excellent ac and dc performance**

10 μV/°C offset drift

10 ppm/°C gain drift

**Qualified for automotive applications**

#### **APPLICATIONS**

High-side current sensing in DC-to-dc converters Motor controls Transmission controls Diesel-injection controls Engine management Suspension controls Vehicle dynamic controls

## **GENERAL DESCRIPTION**

The AD8216 is a single-supply, difference amplifier ideal for amplifying small differential voltages in the presence of large common-mode voltages. The operating input common-mode voltage range extends from -4~V to +65~V. The typical supply voltage is 5~V. The AD8216 features a 3~MHz bandwidth, allowing for the input-to-output propagation delay that is always less than 150~ns. This feature is ideal for applications monitoring rapidly increasing and decreasing load currents.

The AD8216 is offered in a SOIC package. The operating temperature range is -40 °C to +125 °C.

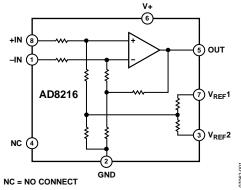

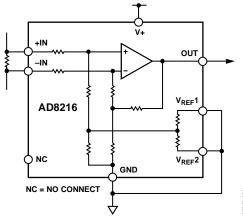

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

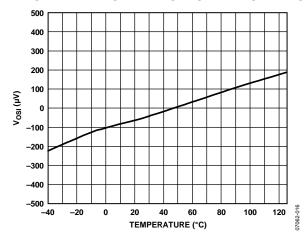

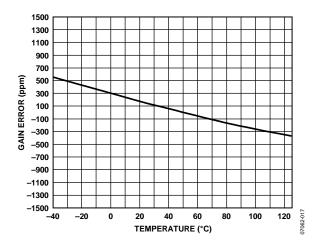

Excellent ac and dc performance over temperature keep errors in the measurement loop to a minimum. Offset and gain drift are guaranteed to a maximum of 20  $\mu V/^{\circ} C$  and 15 ppm/°C, respectively.

The output offset can be adjusted from 0.06 V to 4.9 V with a 5 V supply by using the  $V_{\text{REF}}1$  pin and the  $V_{\text{REF}}2$  pin. With the  $V_{\text{REF}}1$  pin attached to the V+ pin and the  $V_{\text{REF}}2$  pin attached to the GND pin, the output is set at half scale. Attaching both  $V_{\text{REF}}1$  and  $V_{\text{REF}}2$  to GND causes the output to be unipolar, starting near ground. Attaching both  $V_{\text{REF}}1$  and  $V_{\text{REF}}2$  to V+ causes the output to be unipolar, starting near V+. Other offsets can be obtained by applying an external voltage to  $V_{\text{REF}}1$  and  $V_{\text{REF}}2$ .

# **TABLE OF CONTENTS**

| Features 1                                   |

|----------------------------------------------|

| Applications 1                               |

| Functional Block Diagram                     |

| General Description                          |

| Revision History                             |

| Specifications                               |

| Absolute Maximum Ratings                     |

| ESD Caution4                                 |

| Pin Configuration and Function Descriptions5 |

| Typical Performance Characteristics          |

| Theory of Operation                          |

| Output Offset Adjustment                     |

| Unidirectional Operation11                   |

|                                              |

| REVISION HISTORY                             |

| 9/08—Rev. 0 to Rev. A                        |

| Ground Referenced Output11                      |

|-------------------------------------------------|

| V+ Referenced Output                            |

| Bidirectional Operation11                       |

| External ReferenceD Output                      |

| Splitting the Supply                            |

| Splitting an External Reference                 |

| Applications Information                        |

| High-Side Current Sense with a Low-Side Switch  |

| High-Side Current Sense with a High-Side Switch |

| Outline Dimensions                              |

| Ordering Guide14                                |

| 9/08—Rev. 0 to Rev. A            |    |

|----------------------------------|----|

| Changes to Features Section      | 1  |

| Changes to Figure 7              | 6  |

| Changes to Figure 21             | 8  |

| Changes to Table 4 and Figure 25 | 11 |

11/07—Revision 0: Initial Version

# **SPECIFICATIONS**

$T_A$  = operating temperature range,  $V_S$  = 5 V, unless otherwise noted.

Table 1.

| Parameter                          | Conditions                                                          | Min             | Тур  | Max     | Unit         |

|------------------------------------|---------------------------------------------------------------------|-----------------|------|---------|--------------|

| GAIN                               |                                                                     |                 |      |         |              |

| Initial                            |                                                                     |                 | 3    |         | V/V          |

| Accuracy                           | V <sub>OUT</sub> ≥ 0.1 V dc, 25°C                                   |                 |      | ±0.25   | %            |

| Accuracy Over Temperature          | Specified temperature range                                         |                 |      | ±0.4    | %            |

| Gain vs. Temperature               |                                                                     |                 | 10   | 15      | ppm/°C       |

| VOLTAGE OFFSET                     |                                                                     |                 |      |         |              |

| Offset Voltage, RTI                | 25°C                                                                |                 | ±0.5 |         | mV           |

| Over Temperature, RTI              | Specified temperature range                                         |                 |      | ±3      | mV           |

| Offset Drift                       |                                                                     |                 | ±10  | ±20     | μV/°C        |

| INPUT                              |                                                                     |                 |      |         |              |

| Input Impedance                    |                                                                     |                 |      |         |              |

| Differential                       |                                                                     |                 | 400  |         | kΩ           |

| Common Mode                        |                                                                     |                 | 200  |         | kΩ           |

| Input Voltage Range                | Common mode, continuous                                             | -4              |      | +65     | V            |

| , 3 3                              | Differential, V <sub>RFF</sub> 1 and V <sub>RFF</sub> 2 tied to GND |                 | 1.6  |         | V            |

|                                    | Differential, VREF1 @ GND and VREF2 @ 5 V                           | -800            |      | +800    | mV           |

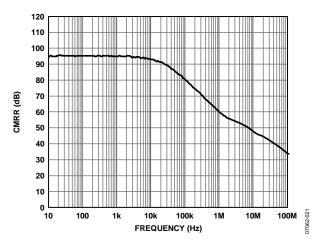

| Common-Mode Rejection              | $25^{\circ}$ C, f = dc to $20 \text{ kHz}^{1}$                      | 80              | 90   |         | dB           |

|                                    | Operating temperature range, $f = dc$ to 20 kHz <sup>1</sup>        | 80              | 90   |         | dB           |

| OUTPUT                             | c personny compensation and graph and a comme                       |                 |      |         |              |

| Output Voltage Range               | $R_L = 25 \text{ k}\Omega$                                          | 0.06            |      | 4.9     | V            |

| Output Resistance                  |                                                                     |                 | 200  |         | Ω            |

| DYNAMIC RESPONSE                   |                                                                     |                 |      |         |              |

| Small Signal –3 dB Bandwidth       |                                                                     |                 | 3    |         | MHz          |

| Slew Rate                          |                                                                     |                 | 15   |         | V/µs         |

| Propagation Delay                  | Input-to-output response                                            |                 | 100  | 150     | ns           |

| NOISE                              |                                                                     |                 |      |         |              |

| 0.1 Hz to 10 Hz, RTI               |                                                                     |                 | 20   |         | μV р-р       |

| Spectral Density, 1 kHz, RTI       |                                                                     |                 | 0.5  |         | μV/√Hz       |

| OFFSET ADJUSTMENT                  |                                                                     |                 |      |         | p. 17 V . 12 |

| Ratiometric Accuracy <sup>2</sup>  | Divider to supplies                                                 | 0.499           |      | 0.501   | V/V          |

| Accuracy, RTO                      | Voltage applied to $V_{REF}1$ and $V_{REF}2$ in parallel            | 01.22           |      | ±0.5    | mV/V         |

| Output Offset Adjustment Range     | $V_s = 5 \text{ V}$                                                 | 0.06            |      | 4.9     | V            |

| VREF Input Voltage Range           |                                                                     | 0.00            |      | $V_{S}$ | v            |

| VREF Divider Resistor Values       |                                                                     | 24              | 32   | 40      | kΩ           |

| POWER SUPPLY                       |                                                                     | 27              | J2   | 70      | 1/22         |

| Operating Range                    |                                                                     | 4.5             |      | 5.5     | V            |

| Quiescent Current Over Temperature | V <sub>оит</sub> = 0.1 V dc                                         | ٠.٦             | 1    | 2       | mA           |

| Power Supply Rejection Ratio       | V <sub>001</sub> – 0.1 V dc                                         | 70              | '    | 2       | dB           |

| TEMPERATURE RANGE                  |                                                                     | 70              |      |         | uв           |

| For Specified Performance          | Operating temperature range                                         | -40             |      | +125    | °C           |

| Tot Specified Fertoffilance        | Operating temperature range                                         | <del>-4</del> 0 |      | +123    |              |

$<sup>^{1}</sup>$  Source imbalance < 2  $\Omega$ .  $^{2}$  The offset adjustment is ratiometric to the power supply when  $V_{REF}1$  and  $V_{REF}2$  are used as a divider between the supplies.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| 14016 2.                              |                 |

|---------------------------------------|-----------------|

| Parameter                             | Rating          |

| Supply Voltage                        | 12.5 V          |

| Continuous Input Common-Mode Voltage  | -40 V to +80 V  |

| Continuous Input Differential Voltage | 6 V             |

| Reverse Supply Voltage                | 0.3 V           |

| ESD Rating                            |                 |

| HBM (Human Body Model)                | ±4000 V         |

| CDM (Charged Device Model)            | ±1000 V         |

| Operating Temperature Range           | -40°C to +125°C |

| Storage Temperature Range             | −65°C to +150°C |

| Output Short-Circuit Duration         | Indefinite      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

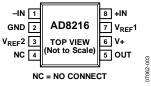

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Metallization Diagram

Figure 3. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic           | Х    | Υ    |

|---------|--------------------|------|------|

| 1       | -IN                | -320 | +390 |

| 2       | GND                | -357 | +14  |

| 3       | V <sub>REF</sub> 2 | -349 | -201 |

| 4       | NC                 | NC   | NC   |

| 5       | OUT                | +348 | -325 |

| 6       | V+                 | +349 | -194 |

| 7       | V <sub>REF</sub> 1 | +349 | -26  |

| 8       | +IN                | +318 | +390 |

Die size is 1100  $\mu m$  by 1035  $\mu m.$

Die thickness is 13 mil.

Minimum passivation opening (minimum bond pad size) is 92  $\mu m \times$  92  $\mu m.$

Passivation type is 8 kA USG (Oxide) + 10 kA Oxynitride.

Bond pad metal composition is 98.5% Al, 1% Si, and 0.5% Cu.

Backside potential is V+.

# TYPICAL PERFORMANCE CHARACTERISTICS

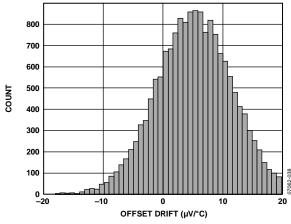

Figure 4. Typical Offset Drift

Figure 5. CMRR vs. Frequency

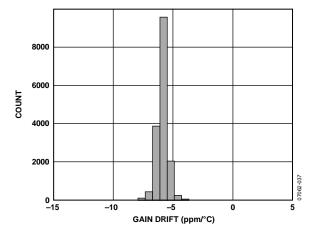

Figure 6. Typical Gain Drift

Figure 7. Typical Small Signal Bandwidth ( $V_{OUT} = 200 \text{ mV } p\text{-}p$ )

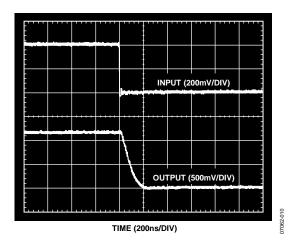

Figure 8. Rise Time

Figure 9. Fall Time

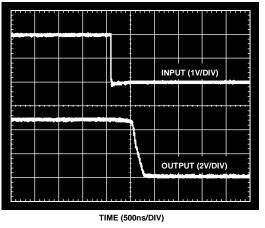

Figure 10. Differential Overload Recovery (Falling)

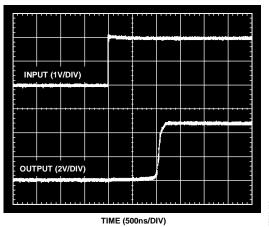

Figure 11. Differential Overload Recovery (Rising)

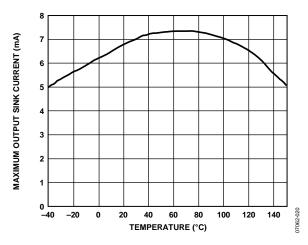

Figure 12. Maximum Output Sink Current vs. Temperature

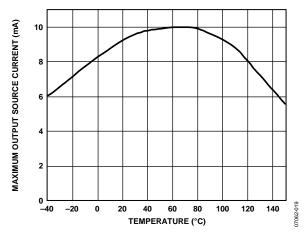

Figure 13. Maximum Output Source Current vs. Temperature

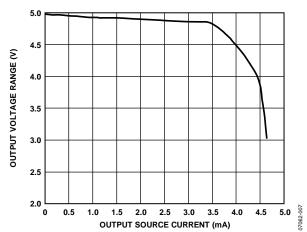

Figure 14. Output Voltage Range vs. Output Source Current

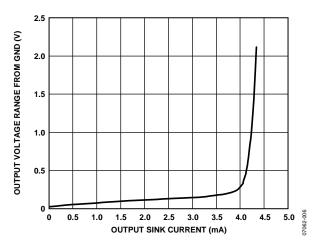

Figure 15. Output Voltage Range from GND vs. Output Sink Current

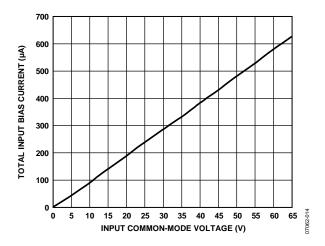

Figure 16. Total Input Bias Current vs. Input Common-Mode Voltage

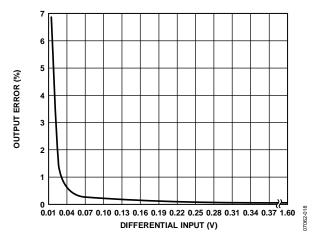

Figure 17. Output Error (%) vs. Differential Input Voltage (Unidirectional Operation (V<sub>REF</sub>1 and V<sub>REF</sub>2 Connected to GND))

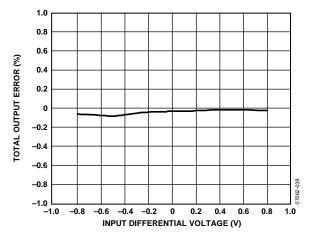

Figure 18. Output Error (%) vs. Differential Input Voltage (Bidirectional Operation ( $V_{REF}1$  and  $V_{REF}2$  Connected to 2.5 V))

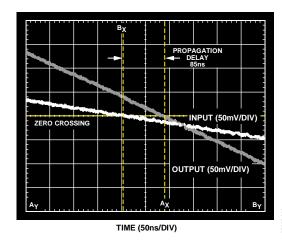

Figure 19. Propagation Delay (Falling)

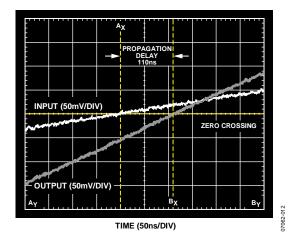

Figure 20. Propagation Delay (Rising)

Figure 21. Gain Drift Distribution

Figure 22. Offset Drift Distribution

## THEORY OF OPERATION

The AD8216 is a single-supply difference amplifier typically used to accurately amplify a small differential current shunt voltage in the presence of a rapidly changing common-mode voltage.

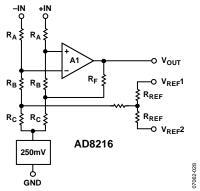

The AD8216 consists of an amplifier (A1), a resistor network, a small voltage reference, and a bias circuit (not shown), see Figure 23.

The set of input attenuators preceding A1 consist of  $R_{\rm A},\,R_{\rm B},$  and  $R_{\rm C},$  which feature a combined series resistance of approximately 200 k $\Omega \pm 20\%$ . The purpose of these resistors is to attenuate the input voltage to match the input voltage range of A1. This balanced resistor network attenuates the common-mode signal by a ratio of 1/18. A1 amplifier inputs are held within the power supply range, even if Pin 1 and Pin 8 exceed the supply or fall below common (ground). A reference voltage of 250 mV biases the attenuator above ground, which allows the amplifier to operate in the presence of negative common-mode voltages.

The input resistor network also attenuates normal (differential) mode voltages. Therefore, Amplifier A1 features a gain of 54 V/V to provide a total system gain of 3V/V.

Total Gain  $(V/V) = 1/18 (V/V) \times 54 (V/V) = 3 V/V$

The reference inputs,  $V_{\text{REF}}1$  and  $V_{\text{REF}}2$ , are tied through resistors to the positive input of A1, which allows the output offset to be adjusted anywhere in the output operating range. The gain is 1 V/V from the reference pins to the output when the reference pins are used in parallel. When they are used to divide the supply, the gain is 0.5 V/V.

The ratios of  $R_A$ ,  $R_B$ ,  $R_C$ , and  $R_F$  are trimmed to a high level of precision to allow the CMRR to exceed 80 dB. This performance is accomplished by laser trimming the resistor ratio matching to better than 0.01%.

Figure 23. Simplified Schematic

## **OUTPUT OFFSET ADJUSTMENT**

The output of the AD8216 can be adjusted for unidirectional or bidirectional operation.

## UNIDIRECTIONAL OPERATION

Unidirectional operation allows the AD8216 to measure currents through a resistive shunt in one direction. The basic modes for unidirectional operation are ground referenced output mode and V+ referenced output mode.

For unidirectional operation, the output can be set at the negative rail (near ground) or at the positive rail (near V+) when the differential input is 0 V. The output moves to the opposite rail when a correct polarity differential input voltage is applied. In this case, full scale is approximately 1.6 V. The required polarity of the differential input depends on the output voltage setting. If the output is set at the positive rail, the input polarity needs to be negative to move the output down. If the output is set at ground, the polarity is positive to move the output up.

## **GROUND REFERENCED OUTPUT**

When using the AD8216 in this mode, both referenced inputs are tied to ground, which causes the output to sit at the negative rail when there are zero differential volts at the input (see Figure 24).

Figure 24. Ground Referenced Output

Table 4. V+=5 V

| V <sub>IN</sub> (Referred to -IN) | V <sub>OUT</sub> |

|-----------------------------------|------------------|

| 0 V                               | 0.1 V            |

| 1.6 V                             | 4.8 V            |

## V+ REFERENCED OUTPUT

The V+ referenced output mode is set when both reference pins are tied to the positive supply. It is typically used when the diagnostic scheme requires detection of the amplifier and the wiring before power is applied to the load (see Figure 25).

Figure 25. V+ Referenced Output

Table 5. V+=5 V

| V <sub>IN</sub> (Referred to –IN) | V <sub>OUT</sub> |

|-----------------------------------|------------------|

| 0 V                               | 4.9 V            |

| −1.6 V                            | 0.1 V            |

#### **BIDIRECTIONAL OPERATION**

Bidirectional operation allows the AD8216 to measure currents through a resistive shunt in two directions.

In this case, the output is set anywhere within the output range. Typically, it is set at half scale for equal range in both directions. In some cases, however, it is set at a voltage other than half scale when the bidirectional current is nonsymmetrical.

Table 6. V+=5 V,  $V_{OUT}=2.5 V$  with  $V_{IN}=0 V$

| V <sub>IN</sub> (Referred to –IN) | V <sub>out</sub> |

|-----------------------------------|------------------|

| +800 mV                           | 4.9 V            |

| −800 mV                           | 0.1V             |

Adjusting the output is accomplished by applying voltage(s) to the referenced inputs.

$V_{\text{REF}}\mathbf{1}$  and  $V_{\text{REF}}\mathbf{2}$  are tied to internal resistors that connect to an internal offset node. There is no operational difference between the pins.

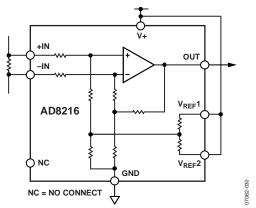

#### **EXTERNAL REFERENCED OUTPUT**

Tying both pins together and to a reference produces an output equal to the reference voltage when there is no differential input (see Figure 26). The output moves down from the reference voltage when the input is negative, relative to the -IN pin, and up when the input is positive, relative to the -IN pin.

Figure 26. External Referenced Output

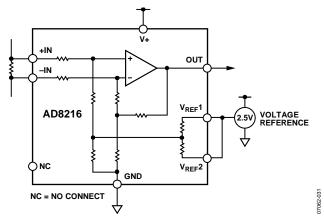

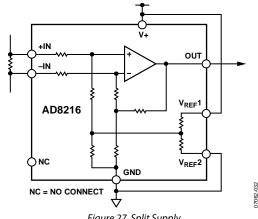

## **SPLITTING THE SUPPLY**

By tying one reference pin to V+ and the other to the ground pin, the output is set at half of the supply when there is no differential input (see Figure 27). The benefit is that no external reference is required to offset the output for bidirectional current measurement. This configuration creates a midscale offset that is ratiometric to the supply, which means that if the supply increases or decreases, the output remains at half the supply. For example, if the supply is 5.0 V, the output is at half scale or 2.5 V. If the supply increases by 10% (to 5.5 V), the output goes to 2.75 V.

Figure 27. Split Supply

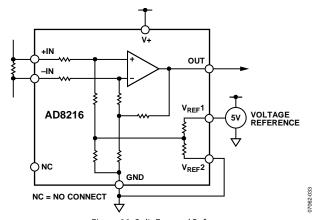

## **SPLITTING AN EXTERNAL REFERENCE**

In this case, an external reference is divided by 2 with an accuracy of approximately 0.5% by connecting one  $V_{\text{REF}}$  pin to ground and the other  $V_{REF}$  pin to the reference (see Figure 28).

Figure 28. Split External Reference

## APPLICATIONS INFORMATION

A typical application for the AD8216 is high-side measurement of a current through a solenoid for PWM control of the solenoid opening. Typical applications include dc-to-dc converters, motor controls, and solenoid controls.

Two typical circuit configurations are used for this type of application.

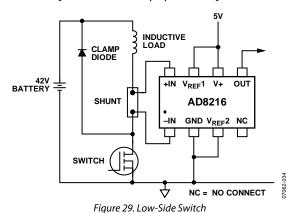

# HIGH-SIDE CURRENT SENSE WITH A LOW-SIDE SWITCH

In this case, the PWM control switch is ground referenced. An inductive load (solenoid) is tied to a power supply. A resistive shunt is placed between the switch and the load (see Figure 29). An advantage of placing the shunt on the high side is that the entire current, including the recirculation current, can be measured because the shunt remains in the loop when the switch is off. In addition, diagnostics can be enhanced because shorts to ground can be detected with the shunt on the high side.

In this circuit configuration, when the switch is closed, the common-mode voltage moves down to near the negative rail. When the switch is opened, the voltage reversal across the inductive load causes the common-mode voltage to be held one diode drop above the battery by the clamp diode.

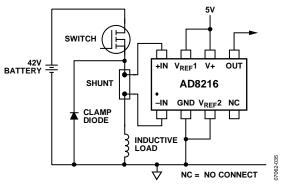

HIGH-SIDE CURRENT SENSE WITH A HIGH-SIDE SWITCH

This configuration minimizes the possibility of unexpected solenoid activation and excessive corrosion (see Figure 30). In this case, both the switch and the shunt are on the high side. When the switch is off, it removes the battery from the load, which prevents damage from potential shorts to ground, while still allowing the recirculating current to be measured and providing for diagnostics. Removing the power supply from the load for the majority of the time minimizes the corrosive effects that could be caused by the differential voltage between the load and ground.

When using a high-side switch, the battery voltage is connected to the load when the switch is closed, causing the common-mode voltage to increase to the battery voltage. In this case, when the switch is opened, the voltage reversal across the inductive load causes the common-mode voltage to be held one diode drop below ground by the clamp diode.

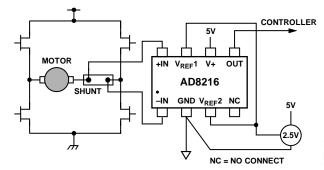

Figure 30. High-Side Switch

Another typical application for the AD8216 is as part of the control loop in H-bridge motor controls. In this case, the AD8216 is placed in the middle of the H-bridge so that it can accurately measure current in both directions by using the shunt available at the motor (see Figure 31). This is a better solution than a ground referenced op amp because ground is not typically a stable reference voltage in this type of application. This instability in the ground reference causes the measurements that could be made with a simple ground referenced op amp to be inaccurate.

The AD8216 measures current in both directions as the H-bridge switches and the motor changes direction. The output of the AD8216 is configured in an external reference bidirectional mode (see the Output Offset Adjustment section).

Figure 31. Motor Control Application

# **OUTLINE DIMENSIONS**

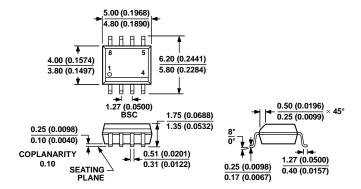

COMPLIANT TO JEDEC STANDARDS MS-012-A A CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 32. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches)

## **ORDERING GUIDE**

| Model                     | Temperature Range | Package Description             | Package Option |

|---------------------------|-------------------|---------------------------------|----------------|

| AD8216YRZ <sup>1</sup>    | -40°C to +125°C   | 8-Lead SOIC_N                   | R-8            |

| AD8216YRZ-RL <sup>1</sup> | -40°C to +125°C   | 8-Lead SOIC_N, 13"Tape and Reel | R-8            |

| AD8216YRZ-R7 <sup>1</sup> | -40°C to +125°C   | 8-Lead SOIC_N, 7"Tape and Reel  | R-8            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**

| AD8216 |  |  |  |

|--------|--|--|--|

| AU0210 |  |  |  |

NOTES