# Quad UV/OV Positive/Negative Voltage Supervisor

**ADM2914**

#### **FEATURES**

Quad UV/OV positive/negative supervisor Supervises up to 2 negative rails

Adjustable UV and OV input thresholds

High threshold accuracy over temperature: ±1.5%

1 V buffered reference output

Open-drain UV and OV reset outputs

Adjustable reset timeout with disable option

Outputs guaranteed down to V<sub>CC</sub> of 1 V

Glitch immunity

62 µA supply current

16-lead QSOP package

#### **APPLICATIONS**

Server supply monitoring

FPGA/DSP core and I/O voltage monitoring

Telecommunications equipment

Medical equipment

#### **GENERAL DESCRIPTION**

The ADM2914 is a quad voltage supervisory IC ideally suited for monitoring multiple rails in a wide range of applications.

Each monitored rail has two dedicated input pins, VHx and VLx, which allows each rail to be monitored for both overvoltage (OV) and undervoltage (UV) conditions. A common active low undervoltage  $(\overline{UV})$  and overvoltage  $(\overline{OV})$  pin is shared by each of the monitored voltage rails.

The ADM2914 includes a 1 V buffered reference output, REF, that acts as an offset when monitoring a negative voltage. The three-state SEL pin determines the polarity of the third and fourth inputs, that is, it configures the device to monitor positive or negative supplies.

The device incorporates an internal shunt regulator that enables the device to be used in higher voltage systems. This feature requires a resistor to be placed between the main supply rail and

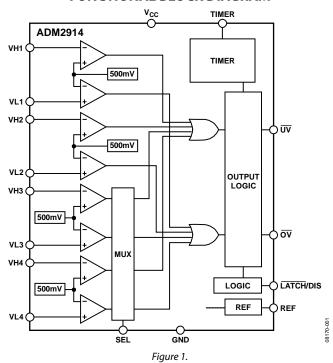

#### **FUNCTIONAL BLOCK DIAGRAM**

the  $V_{\rm CC}$  pin to limit the current flow into the  $V_{\rm CC}$  pin to no greater than 10 mA. The ADM2914 uses the internal shunt regulator to regulate  $V_{\rm CC}$  if the supply line exceeds the absolute maximum ratings.

The ADM2914 is available in two models. The ADM2914-1 offers a latching overvoltage output that can be cleared by toggling the  $\overline{LATCH}$  input pin. The ADM2914-2 has a disable pin that can override and disable both the  $\overline{OV}$  and  $\overline{UV}$  output signals.

The ADM2914 is available in a 16-lead QSOP package. The device operates over the extended temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

# **TABLE OF CONTENTS**

| Features                                     |          |

|----------------------------------------------|----------|

| Applications                                 |          |

| Functional Block Diagram                     |          |

| General Description                          |          |

| Revision History                             | 2        |

| Specifications                               | 3        |

| Absolute Maximum Ratings                     | 4        |

| ESD Caution                                  | 4        |

| Pin Configurations and Function Descriptions | !        |

| Typical Performance Characteristics          | 6        |

| Theory of Operation                          | 8        |

| Voltage Supervision                          | 8        |

| Polarity Configuration                       | 8        |

| Monitoring Pin Connections                   | <u>ç</u> |

| Threshold Accuracy                           |          |

| Voltage Monitoring Example                                            | 10 |

|-----------------------------------------------------------------------|----|

| Power-Up and Power-Down                                               | 11 |

| UV/OV Timing Characteristics                                          | 11 |

| Timer Capacitor Selection                                             | 11 |

| $\overline{\text{UV}}$ and $\overline{\text{OV}}$ Rise and Fall Times | 12 |

| UV/OV Output Characteristics                                          | 12 |

| Glitch Immunity                                                       | 12 |

| Undervoltage Lockout (UVLO)                                           | 12 |

| Shunt Regulator                                                       | 12 |

| OV Latch (ADM2914-1)                                                  | 12 |

| Disable (ADM2914-2)                                                   | 12 |

| Typical Applications                                                  | 13 |

| Outline Dimensions                                                    |    |

| Ordering Guide                                                        | 15 |

#### **REVISION HISTORY**

5/09—Revision 0: Initial Version

# **SPECIFICATIONS**

$T_A = -40$ °C to +85°C. Typical values at  $T_A = 25$ °C, unless otherwise noted.  $V_{CC} = 3.3$  V, VLx = 0.45 V, VHx = 0.55 V,  $\overline{LATCH} = V_{CC}$ ,  $SEL = V_{CC}$ , DIS = open, unless otherwise noted.

Table 1.

| Table 1.                                                                      | Min   | Tvn  | Max                | Hnit | Test Conditions/Comments                                         |

|-------------------------------------------------------------------------------|-------|------|--------------------|------|------------------------------------------------------------------|

| Parameter CHIATOR                                                             | Min   | Тур  | IVIAX              | Unit | rest Conditions/Comments                                         |

| SHUNT REGULATOR                                                               | 6.3   |      | 6.0                | .,   |                                                                  |

| V <sub>CC</sub> Shunt Regulator Voltage, V <sub>SHUNT</sub>                   | 6.2   | 6.6  | 6.9                | V    | $I_{cc} = 5 \text{ mA}$                                          |

| V. Chunt Dogulator Load Dogulation AV                                         | 6.2   | 6.6  | 7.0                | V    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| V <sub>CC</sub> Shunt Regulator Load Regulation, ΔV <sub>SHUNT</sub>          |       | 200  | 300                | mV   | $I_{CC} = 2 \text{ mA to } 10 \text{ mA}$                        |

| SUPPLY 1                                                                      | 2.2   |      |                    | .,   |                                                                  |

| Supply Voltage, V <sub>Cc</sub> <sup>1</sup>                                  | 2.3   |      | V <sub>SHUNT</sub> | V    | DIS OV                                                           |

| Minimum V <sub>CC</sub> Output Valid, V <sub>CCR(MIN)</sub>                   | 1.0   | 2    | 1                  | V    | DIS = 0 V                                                        |

| Supply Undervoltage Lockout, V <sub>CC(UVLO)</sub>                            | 1.9   | 2    | 2.1                | ٧,,  | DIS = $0 \text{ V}$ , $V_{CC}$ rising                            |

| Supply Undervoltage Lockout Hysteresis, ΔV <sub>CC(HYST)</sub>                | 5     | 25   | 50                 | mV   | DIS = 0 V                                                        |

| Supply Current, I <sub>CC</sub>                                               |       | 62   | 100                | μΑ   | $V_{CC} = 2.3 \text{ V to 6 V}$                                  |

| REFERENCE OUTPUT                                                              |       |      |                    |      |                                                                  |

| Reference Output Voltage, V <sub>REF</sub>                                    | 0.985 | 1    | 1.015              | V    | $I_{VREF} = \pm 1 \text{ mA}$                                    |

|                                                                               | 0.985 | 1    | 1.020              | V    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| UNDERVOLTAGE/OVERVOLTAGE CHARACTERISTICS                                      |       |      |                    |      |                                                                  |

| Undervoltage/Overvoltage Threshold, V <sub>UOT</sub>                          | 492.5 | 500  | 507.5              | mV   |                                                                  |

| Undervoltage/Overvoltage Threshold to Output Delay, $t_{\text{UOD}}$          | 50    | 125  | 500                | μs   | $VHx = V_{UOT} - 5 \text{ mV or } VLx = V_{UOT} + 5 \text{ mV}$  |

| VHx, VLx Input Current, I <sub>VHL</sub>                                      |       |      | ±15                | nA   |                                                                  |

|                                                                               |       |      | ±30                | nA   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| $\overline{\text{UV}}/\overline{\text{OV}}$ Timeout Period, $t_{\text{UOTO}}$ | 6     | 8.5  | 12.5               | ms   | $C_{TIMER} = 1 \text{ nF}$                                       |

|                                                                               | 6     | 8.5  | 14                 | ms   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| OV LATCH CLEAR INPUT (ADM2914-1)                                              |       |      |                    |      |                                                                  |

| OV Latch Clear Threshold Input High, V <sub>LATCH(IH)</sub>                   | 1.2   |      |                    | V    |                                                                  |

| OV Latch Clear Threshold Input Low, VTATCH(II)                                |       |      | 0.8                | V    |                                                                  |

| LATCH Input Current, I <sub>LATCH</sub>                                       |       |      | ±1                 | μA   | $V_{LATCH} > 0.5 V$                                              |

| DISABLE INPUT (ADM2914-2)                                                     |       |      |                    |      |                                                                  |

| DIS Input High, V <sub>DIS(IH)</sub>                                          | 1.2   |      |                    | V    |                                                                  |

| DIS Input Low, V <sub>DIS(IL)</sub>                                           |       |      | 0.8                | V    |                                                                  |

| DIS Input Current, I <sub>DIS</sub>                                           | 1     | 2    | 3                  | μΑ   | V <sub>DIS</sub> > 0.5 V                                         |

| TIMER CHARACTERISTICS                                                         |       |      |                    |      | DIS                                                              |

| TIMER Pull-Up Current, I <sub>TIMER(UP)</sub>                                 | -1.3  | -2.1 | -2.8               | μΑ   | V <sub>TIMER</sub> = 0 V                                         |

| ····-·                                                                        | -1.2  | -2.1 | -2.8               | μA   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| TIMER Pull-Down Current, I <sub>TIMER(DOWN)</sub>                             | 1.3   | 2.1  | 2.8                | μA   | V <sub>TIMER</sub> = 1.6 V                                       |

| ····Imer(DOWN)                                                                | 1.2   | 2.1  | 2.8                | μA   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| TIMER Disable Voltage, V <sub>TIMER(DIS)</sub>                                | -180  | -270 | 2.0                | mV   | Referenced to $V_{CC}$                                           |

| OUTPUT VOLTAGE                                                                |       |      |                    |      |                                                                  |

| Output Voltage High, UV/OV, V <sub>OH</sub>                                   | 1     |      |                    | ٧    | $V_{CC} = 2.3 \text{ V}; I_{\overline{UV/OV}} = -1  \mu\text{A}$ |

| Output Voltage Low, UV/OV, V <sub>OI</sub>                                    |       | 0.1  | 0.3                | V    | $V_{CC} = 2.3 \text{ V}; I_{\overline{UV/OV}} = 2.5 \text{ mA}$  |

| output voltage Low, 5 v, 5 v, v <sub>ol</sub>                                 |       | 0.01 | 0.15               | V    | $V_{CC} = 1 \text{ V}; I_{UV} = 100  \mu\text{A}$                |

| TURES CTATE INDUIT CEI                                                        |       | 0.01 | 0.15               | V    | $V_{CC} = 1 \text{ V}, I_{\overline{UV}} = 100 \mu\text{A}$      |

| THREE-STATE INPUT SEL                                                         |       |      | 0.4                | .,   |                                                                  |

| Low Level Input Voltage, V <sub>IL</sub>                                      | 1.4   |      | 0.4                | V    |                                                                  |

| High Level Input Voltage, V <sub>IH</sub>                                     | 1.4   | 0.0  | 1.1                | V    |                                                                  |

| Pin Voltage When Left in High-Z State, $V_z$                                  | 0.7   | 0.9  | 1.1                | V    | $I_{SEL} = \pm 10 \mu\text{A}$                                   |

| CELLE L. C. C.                                                                | 0.6   | 0.9  | 1.2                | V    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$             |

| SEL High, Low Input Current, I <sub>SEL</sub>                                 |       |      | ±25                | μA   | GEL III IV GNG                                                   |

| Maximum SEL Input Current, I <sub>SEL(MAX)</sub>                              |       |      | ±30                | μΑ   | SEL tied to V <sub>cc</sub> or GND                               |

$<sup>^1</sup>$  The maximum voltage on the  $V_{CC}$  pin is limited by the input current. The  $V_{CC}$  pin has an internal 6.5 V shunt regulator and, therefore, a low impedance supply greater than 6 V may exceed the maximum allowed input current. When operating from a higher supply than 6 V, always use a dropping resistor.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Tuble 2.                                   |                                               |

|--------------------------------------------|-----------------------------------------------|

| Parameter                                  | Rating                                        |

| V <sub>cc</sub>                            | −0.3 V to +6 V                                |

| UV, OV                                     | −0.3 V to +16 V                               |

| TIMER                                      | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V})$ |

| VLx, VHx, LATCH, DIS, SEL                  | −0.3 V to +7.5 V                              |

| I <sub>cc</sub>                            | 10 mA                                         |

| Reference Load Current (I <sub>REF</sub> ) | ±1 mA                                         |

| I <sub>UV</sub> , I <sub>OV</sub>          | 10 mA                                         |

| Storage Temperature Range                  | −65°C to +150°C                               |

| Operating Temperature Range                | -40°C to +125°C                               |

| Lead Temperature (Soldering, 10 sec)       | 300°C                                         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 3. Thermal Resistance**

| Package Type | $\theta_{JA}$ | Unit |  |

|--------------|---------------|------|--|

| 16-Lead QSOP | 104           | °C/W |  |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

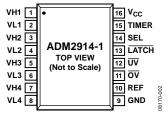

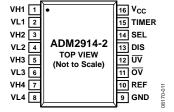

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 2. ADM2914-1 Pin Configuration

Figure 3. ADM2914-2 Pin Configuration

**Table 4. Pin Function Descriptions**

| Mnemonic |                 | -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | ADM2914-1       | ADM2914-2       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1        | VH1             | VH1             | Voltage High Input 1 and Voltage High Input 2. If the voltage monitored by VH1 or VH2 drops                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3        | VH2             | VH2             | below 0.5 V, an undervoltage condition is detected. Connect to V <sub>CC</sub> when not in use.                                                                                                                                                                                                                                                                                                                                                                                                |

| 2        | VL1             | VL1             | Voltage Low Input 1 and Voltage Low Input 2. If the voltage monitored by VL1 or VL2 rises above                                                                                                                                                                                                                                                                                                                                                                                                |

| 4        | VL2             | VL2             | 0.5 V, an overvoltage condition is detected. Tie to GND when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5        | VH3             | VH3             | Voltage High Input 3 and Voltage High Input 4. The polarity of these inputs is determined by the                                                                                                                                                                                                                                                                                                                                                                                               |

| 7        | VH4             | VH4             | state of the SEL pin (see Table 5). When the monitored input is configured as a positive voltage and the voltage monitored by VH3 or VH4 drops below 0.5 V, an undervoltage condition is detected. Conversely, when the input is configured as a negative voltage and the input drops below 0.5 V, an overvoltage condition is detected. Connect to V <sub>CC</sub> when not in use.                                                                                                           |

| 6        | VL3             | VL3             | Voltage Low Input 3 and Voltage Low Input 4. The polarity of these inputs is determined by the                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8        | VL4             | VL4             | state of the SEL pin (see Table 5). When the monitored input is configured as a positive voltage and the voltage monitored by VL3 or VL4 rises above 0.5 V, an overvoltage condition is detected. Conversely, when the input is configured as a negative voltage and the input rises above 0.5 V, an undervoltage condition is detected. Tie to GND when not in use.                                                                                                                           |

| 9        | GND             | GND             | Device Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10       | REF             | REF             | Buffered Reference Output. This pin is a 1 V reference that is used as an offset when monitoring negative voltages. This pin can source or sink 1 mA, and drive loads up to 1 nF. Larger capacitive loads may lead to instability. Leave unconnected when not in use.                                                                                                                                                                                                                          |

| 11       | ŌV              | ŌV              | Overvoltage Reset Output. $\overline{OV}$ is asserted low if a negative polarity input voltage drops below its associated threshold or if a positive polarity input voltage exceeds its threshold. The ADM2914-1 allows $\overline{OV}$ to be latched low. The ADM2914-2 holds $\overline{OV}$ low for an adjustable timeout period determined by the TIMER capacitor. This pin has a weak pull-up to VCC and can be pulled up to 16 V externally. Leave this pin unconnected when not in use. |

| 12       | ŪV              | ŪV              | Undervoltage Reset Output. UV is asserted low if a negative polarity input voltage exceeds its associated threshold or if a positive polarity input voltage drops below its threshold. UV is held low for an adjustable timeout period set by the external capacitor tied to the TIMER pin. The UV pin has a weak pull-up to V <sub>CC</sub> and can be pulled up to 16 V externally via an external pull-up resistor. Leave this pin unconnected when not in use.                             |

| 13       | LATCH           |                 | OV Latch Bypass Input/Clear Pin. When pulled high, the OV latch is cleared. When held high, the OV output has the same delay and output characteristics as the UV output. When pulled low, the OV output is latched when asserted. (Applies only to the ADM2914-1.)                                                                                                                                                                                                                            |

|          |                 | DIS             | $\overline{OV}$ and $\overline{UV}$ Disable Input. When pulled high, the $\overline{OV}$ and $\overline{UV}$ outputs are held high irrespective of the state of the VHx and VLx input pins. However, if a UVLO condition occurs, the $\overline{OV}$ and $\overline{UV}$ outputs are asserted. This pin has a weak internal pull-down (2 $\mu$ A) to GND. Leave this pin unconnected when not in use. (Applies only to the ADM2914-2.)                                                         |

| 14       | SEL             | SEL             | Input Polarity Select. This three-state input pin allows the polarity of VH3, VL3, VH4, and VL4 to be configured. Connect to V <sub>CC</sub> or GND, or leave open to select one of three possible input polarity configurations (see Table 5).                                                                                                                                                                                                                                                |

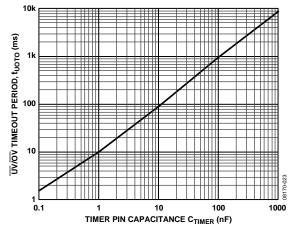

| 15       | TIMER           | TIMER           | Adjustable Reset Delay Timer. Connect an external capacitor to the TIMER pin to program the reset timeout delay. Refer to Figure 15 in the Typical Performance Characteristics section. Connect this pin to $V_{CC}$ to bypass the timer.                                                                                                                                                                                                                                                      |

| 16       | V <sub>cc</sub> | V <sub>cc</sub> | Supply Voltage. $V_{CC}$ operates as a direct supply for voltages up to 6 V. For voltages greater than 6 V, it operates as a shunt regulator. A dropping resistor must be used in this configuration to limit the current to less than 10 mA. When used without the resistor, the voltage at this pin must not exceed 6 V. A 0.1 $\mu$ F bypass capacitor or greater should be used.                                                                                                           |

# TYPICAL PERFORMANCE CHARACTERISTICS

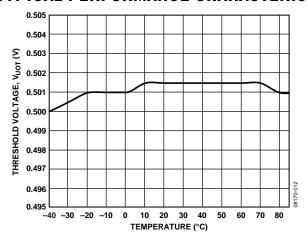

Figure 4. Input Threshold Voltage vs. Temperature

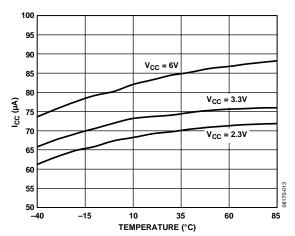

Figure 5. Supply Current vs. Temperature

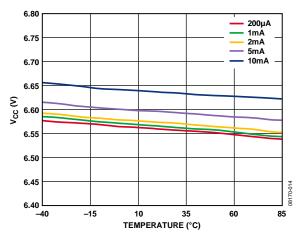

Figure 6. Vcc Shunt Voltage vs. Temperature

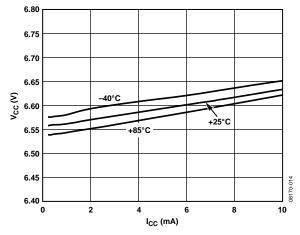

Figure 7. Vcc Shunt Voltage vs. Icc

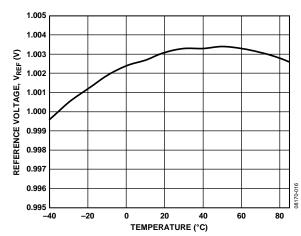

Figure 8. Buffered Reference Voltage vs. Temperature

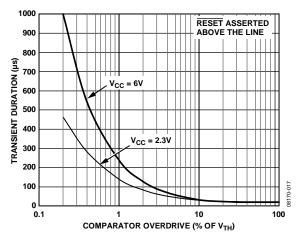

Figure 9. Transient Duration vs. Comparator Overdrive

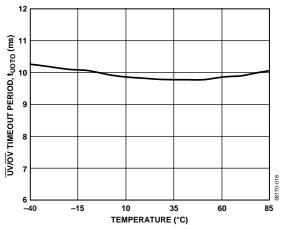

Figure 10. UV/OV Timeout Period vs. Temperature

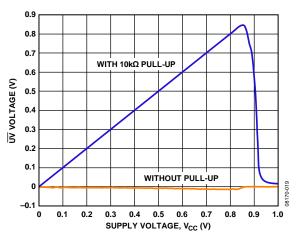

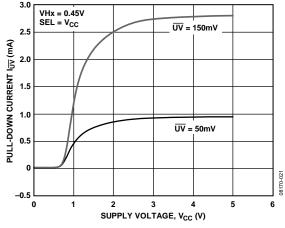

Figure 11.  $\overline{UV}$  Output Voltage vs.  $V_{CC}$

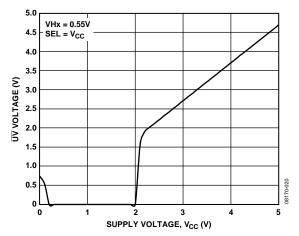

Figure 12.  $\overline{UV}$  Output Voltage vs.  $V_{CC}$

Figure 13.  $I_{SINK}$ ,  $I_{\overline{UV}}$  vs.  $V_{CC}$

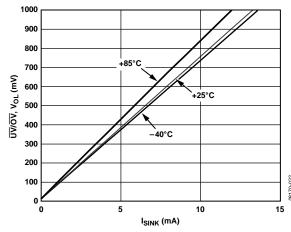

Figure 14. UV/OV Voltage Output Low vs. Output Sink Current

Figure 15. UV/OV Timeout Period vs. Capacitance

# THEORY OF OPERATION VOLTAGE SUPERVISION

The ADM2914 supervises up to four voltage rails for overvoltage and undervoltage conditions. Two pins, VHx and VLx, are assigned to monitor each rail, one for overvoltage detection and the other for undervoltage detection. Each pin is connected to the input of an internal voltage comparator, and its voltage level is internally compared with a 0.5 V voltage reference with accuracy of  $\pm 1.5\%$ .

The output of each of the internal undervoltage comparators is tied to a common  $\overline{UV}$  output pin. Likewise, the outputs of the internal overvoltage comparators are tied to a common  $\overline{OV}$  output pin.

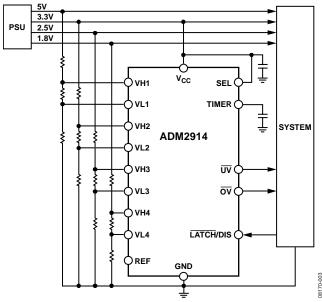

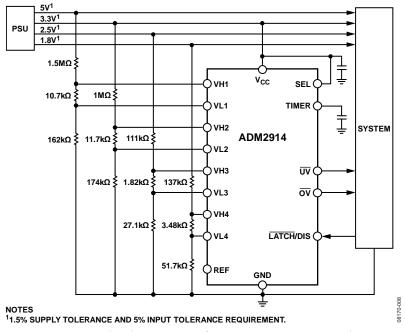

Figure 16. Typical Applications Diagram

#### **POLARITY CONFIGURATION**

The ADM2914 is capable of monitoring supply voltages of both positive and negative polarities. The SEL pin is a three-state pin that determines the polarity of Input 3 and Input 4. As summarized in Table 5, the SEL pin is either connected to GND,  $V_{\rm CC}$ , or left unconnected.

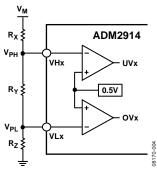

When an input is configured to monitor a positive voltage, using the three-resistor scheme shown in Figure 17, VHx is connected to the high-side tap of the resistor divider and VLx is connected to the low-side tap of the resistor divider.

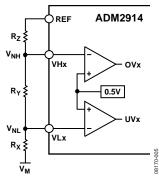

Conversely, when an input is configured to monitor a negative voltage, UVx and OVx are swapped internally. The negative voltage for monitoring is then connected as shown in Figure 18. VHx is still connected to the high-side tap and VLx is still connected to the low-side tap. Within this configuration, an undervoltage condition occurs when the monitored voltage is less negative than the programmed threshold, and an overvoltage condition occurs when the monitored voltage is more negative than the configured threshold.

**Table 5. Polarity Configuration**

|                              | Input 3  |              |              | Input 4  |              |              |

|------------------------------|----------|--------------|--------------|----------|--------------|--------------|

| SEL Pin                      | Polarity | UV Condition | OV Condition | Polarity | UV Condition | OV Condition |

| Connected to V <sub>CC</sub> | Positive | VH3 < 0.5 V  | VL3 > 0.5 V  | Positive | VH4 < 0.5 V  | VL4 > 0.5 V  |

| Left Unconnected             | Positive | VH3 < 0.5 V  | VL3 > 0.5 V  | Negative | VL4 > 0.5 V  | VH4 < 0.5 V  |

| Connected to GND             | Negative | VL3 > 0.5 V  | VH3 < 0.5 V  | Negative | VL4 > 0.5 V  | VH4 < 0.5 V  |

#### MONITORING PIN CONNECTIONS

#### Positive Voltage Monitoring Scheme

When monitoring a positive supply, the desired nominal operating voltage for monitoring is denoted by  $V_{\rm M}$ ,  $I_{\rm M}$  is the nominal current through the resistor divider,  $V_{\rm OV}$  is the overvoltage trip point, and  $V_{\rm UV}$  is the undervoltage trip point.

Figure 17. Positive Undervoltage/Overvoltage Monitoring Configuration

Figure 17 illustrates the positive voltage monitoring input connection. Three external resistors,  $R_{\rm X}$ ,  $R_{\rm Y}$ , and  $R_{\rm Z}$ , divide the positive voltage for monitoring,  $V_{\rm M}$ , into high-side voltage,  $V_{\rm PH}$ , and low-side voltage,  $V_{\rm PL}$ . The high-side voltage is connected to the corresponding VHx pin, and the low-side voltage is connected to the corresponding VLx pin.

To trigger an overvoltage condition, the low-side voltage (in this case,  $V_{\text{PL}}$ ) must exceed the 0.5 V threshold on the VLx pin. The low-side voltage,  $V_{\text{PI}}$ , is given by the following equation:

$$V_{PL} = V_{OV} \left( \frac{R_Z}{R_X + R_Y + R_Z} \right) = 0.5 \text{ V}$$

Also,

$$R_X + R_Y + R_Z = \frac{V_M}{I_M}$$

Therefore, R<sub>z</sub>, which sets the desired trip point for the overvoltage monitor, is calculated using the following equation:

$$R_Z = \frac{(0.5)(V_M)}{(V_{OV})(I_M)} \tag{1}$$

To trigger the undervoltage condition, the high-side voltage,  $V_{\rm PH}$ , must exceed the 0.5 V threshold on the VHx pin. The high-side voltage,  $V_{\rm PH}$ , is given by the following equation:

$$V_{PH} = V_{UV} \left( \frac{R_Y + R_Z}{R_X + R_Y + R_Z} \right) = 0.5 \text{ V}$$

Because R<sub>z</sub> is already known, R<sub>y</sub> can be expressed as follows:

$$R_{Y} = \frac{(0.5)(V_{M})}{(V_{UV})(I_{M})} - R_{Z}$$

(2)

When  $R_Y$  and  $R_Z$  are known,  $R_X$  is calculated using the following equation:

$$R_X = \frac{(V_M)}{(I_M)} - R_Z - R_Y \tag{3}$$

If  $V_M$ ,  $I_M$ ,  $V_{OV}$ , or  $V_{UV}$  changes, each step must be recalculated.

#### **Negative Voltage Monitoring Scheme**

Figure 18 shows the circuit configuration for negative supply voltage monitoring. To monitor the negative voltage, a 1 V reference voltage is required to connect to the end node of the voltage divider circuit. This reference voltage is generated internally and is output through the REF pin.

Figure 18. Negative Undervoltage/Overvoltage Monitoring Configuration

The equations described in the Positive Voltage Monitoring Scheme section need some minor modifications for use with negative voltage monitoring. The 1 V reference voltage is added to the overall voltage drop; it must therefore be subtracted from  $V_{My}$ ,  $V_{UV}$ , and  $V_{OV}$  before using each in the previous equations.

To monitor a negative voltage level, the resistor divider circuit divides the voltage differential level between the 1 V reference voltage and the negative supply voltage into high-side voltage,  $V_{\rm NH}$ , and low-side voltage,  $V_{\rm NL}$ . Similar to the positive voltage monitoring scheme, the high-side voltage,  $V_{\rm NH}$ , is connected to the corresponding VH $_{\rm X}$  pin, and the low-side voltage,  $V_{\rm NL}$ , is connected to the corresponding VL $_{\rm X}$  pin. Refer to the Voltage Monitoring Example section for more information.

#### THRESHOLD ACCURACY

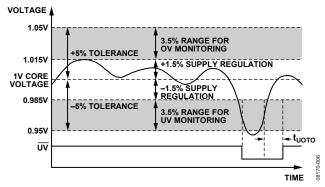

The reset threshold accuracy is fundamental, especially at lower voltage levels. Consider an FPGA application that requires a 1 V core voltage input with tolerance of  $\pm 5\%$ , where the supply has a specified regulation, for example,  $\pm 1.5\%$ . As shown in Figure 19, to ensure that the supply is within the FPGA input voltage requirement range, its voltage level must be monitored for UV and OV conditions. The voltage swing on the supply itself causes the voltage band available for setting the monitoring threshold to be quite narrow. In this example, the threshold voltages, including the tolerances, must fit within a monitor region of only 0.035 V. The ADM2914 device with 0.1% resistors can achieve this level of accuracy.

Figure 19. Monitoring Threshold Accuracy Example

#### **VOLTAGE MONITORING EXAMPLE**

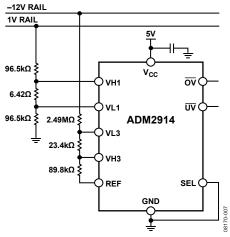

To illustrate how the ADM2914 device works in a real application, consider the 1 V input example shown in Figure 19, with the addition of a -12 V rail.

The first step is to choose the nominal current flow through both voltage divider circuits, for example, 5  $\mu$ A.

For the 1 V  $\pm$  5% input, due to the specified  $\pm$ 1.5% regulation of the supply, the UV and OV thresholds should be set in the middle of the voltage monitoring band. In this case, on the  $\pm$ 3.25% points of the supply, the UV threshold is 0.9675 V and the OV threshold is 1.0325 V.

Input these values into Equation 1.

$$R_Z = \frac{(0.5)(1)}{(1.0325)(5 \times 10^{-6})} \approx 96.5 \text{ k}\Omega$$

Insert the value of  $R_Z$  into Equation 2.

$$R_{_Y} = \frac{(0.5)(1)}{(0.9675)(5\times10^{-6})} - 96.5 \text{ k}\Omega \approx 6.42 \text{ k}\Omega$$

Then substitute the calculated values for  $R_Z$  and  $R_Y$  into Equation 3.

$$R_X = \frac{1}{5 \times 10^{-6}} - 96.5 \text{ k}\Omega - 6.42 \text{ k}\Omega \approx 96.5 \text{ k}\Omega$$

This design approach meets the application specifications. As described previously, the 1 V rail is specified with an input requirement of  $\pm 5\%$  and a supply tolerance of  $\pm 1.5\%$ . This effectively means that the OV threshold of the monitoring

device, including all the tolerance factors, must fit within the 1.015~V to 1.05~V range. Similarly, the UV threshold range must be between 0.95~V and 0.985~V.

The four worst-case scenarios of minimum and maximum undervoltage and overvoltage thresholds are calculated as follows:

Minimum overvoltage threshold

$$\begin{split} V_{OV\_MIN} &= (0.5 \text{ V} - 1.5\%) \left( 1 + \frac{(R_X - 0.1\%) + (R_Y - 0.1\%)}{\left( R_Z + 0.1\% \right)} \right) \\ &= 0.4925 \left( 1 + \frac{(96,500 + 6420)(0.999)}{(96,500)(1.001)} \right) \\ &= 1.016 \text{ V} > 1.015 \text{ V} \end{split}$$

Maximum overvoltage threshold

$$V_{OV\_MAX} = (0.5 \text{ V} + 1.5\%) \left( 1 + \frac{(R_X + 0.1\%) + (R_Y + 0.1\%)}{(R_Z - 0.1\%)} \right)$$

= 1.049 V < 1.05 V

The maximum and minimum overvoltage threshold values lie within the 1.015 V to 1.05 V range specified. The minimum and maximum undervoltage thresholds are calculated as follows:

Minimum undervoltage threshold

$$V_{UV\_MIN} = (0.5 \text{ V} - 1.5\%) \left( 1 + \frac{(R_X - 0.1\%)}{(R_Y + 0.1\%) + (R_Z + 0.1\%)} \right)$$

= 0.953 V > 0.95 V

Maximum undervoltage threshold

$$\begin{split} &V_{UV\_MAX} = (0.5 \text{ V} + 1.5\%) \left( 1 + \frac{(R_X + 0.1\%)}{(R_Y - 0.1\%) + (R_Z - 0.1\%)} \right) \\ &= 0.984 \text{ V} < 0.985 \text{ V} \end{split}$$

Again, these values fit within the specified undervoltage monitoring range. All four worst-case scenarios satisfy the tolerance requirement; therefore, the design approach is valid.

Figure 20. Positive and Negative Supply Monitor Example

Next, consider a -12~V input, which is specified with a  $\pm 20\%$  input. The threshold accuracy required by the supply is chosen to be within  $\pm 5\%$  of the -12~V rail. Therefore, the overvoltage threshold is set to -13.5~V, and the undervoltage threshold is -10.5~V. The negative voltage scheme configuration requires that the 1~V reference voltage be accounted for in Equation 1 to Equation 3. The 1~V reference voltage is subtracted from  $V_{\rm M}$ ,  $V_{\rm UV}$ , and  $V_{\rm OV}$ , and the absolute value of the result is taken.

Equation 1 becomes

$$R_Z = \frac{(0.5)(|-12-1|)}{(|-13.5-1|)(5\times10^{-6})} \approx 89.8 \text{ k}\Omega$$

Insert the value of  $R_Z$  into Equation 2.

$$R_{Y} = \frac{(0.5)(-12-1)}{(-10.5-1)(5\times10^{-6})} - 89.8 \text{ k}\Omega \approx 23.4 \text{ k}\Omega$$

To calculate R<sub>x</sub>, insert the value of R<sub>z</sub> and R<sub>y</sub> into Equation 3.

$$R_X = \frac{(|-12-1|)}{5 \times 10^{-6}} - (89.8 \text{ k}\Omega) - (23.4 \text{ k}\Omega) \approx 2.49 \text{ M}\Omega$$

#### **POWER-UP AND POWER-DOWN**

On power-up, when  $V_{CC}$  reaches 1 V, the active low  $\overline{UV}$  output is asserted, and the  $\overline{OV}$  output pulls up to  $V_{CC}$ . When the voltage on the  $V_{CC}$  pin reaches 1 V, the ADM2914 is guaranteed to assert  $\overline{UV}$  low and  $\overline{OV}$  high. When  $V_{CC}$  exceeds 1.9 V (minimum), the VHx and VLx inputs take control. When  $V_{CC}$  and each of the VHx inputs are valid, an internal timer begins. Subsequent to an adjustable time delay,  $\overline{UV}$  weakly pulls high.

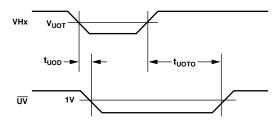

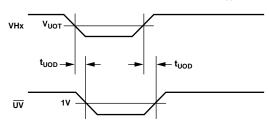

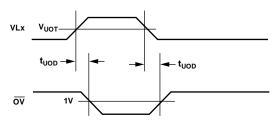

#### **UV/OV** TIMING CHARACTERISTICS

$\overline{UV}$  is an active low output. It is asserted when any of the four monitored voltages is below its associated threshold. When the voltage on the  $V_{CC}$  pin is above 2 V, an internal timer holds  $\overline{UV}$  low for an adjustable period,  $t_{UOTO}$ , after the voltage on all the monitoring rails rises above their thresholds. This allows time for all monitored power supplies to stabilize after power-up. Similarly, any monitored voltage that falls below its threshold initiates a timer reset, and the timer starts again when all the monitoring rails rise above their thresholds.

The  $\overline{\text{UV}}$  and  $\overline{\text{OV}}$  outputs are held asserted after all faults have cleared for an adjustable timeout period, determined by the value of the external capacitor attached to the TIMER pin.

#### **TIMER CAPACITOR SELECTION**

The  $\overline{UV}$  and  $\overline{OV}$  timeout period on the ADM2914 is programmable via the external timer capacitor,  $C_{TIMER}$ , placed between the TIMER pin and ground. The timeout period,  $t_{UOTO}$ , is calculated using the following equation:

$$C_{TIMER} = (t_{IJOTO})(115)(10^{-9})$$

F/sec

Refer to Figure 15 in the Typical Performance Characteristics section, which illustrates the delay time as a function of the timer capacitor value. A minimum capacitor value of 10 pF is required. The chosen timer capacitor must have a leakage current that is less than the 1.3  $\mu A$  TIMER pin charging current. To bypass the timeout period, connect the TIMER pin to  $V_{\rm CC}$ .

#### VHx MONITOR TIMING

#### VHx MONITOR TIMING (TIMER PIN TIED TO VCC)

WHEN AN INPUT IS CONFIGURED TO MONITOR A NEGATIVE VOLTAGE, VHX WILL TRIGGER AN OVERVOLTAGE CONDITION.

R AN OVERVOLTAGE CONDITION.

Figure 21. VHx Positive Voltage Monitoring Timing Diagram

VLx MONITOR TIMING

# VLx V<sub>UOT</sub> t<sub>UOTO</sub> T

#### VLx MONITOR TIMING (TIMER PIN TIED TO V<sub>CC</sub>)

WHEN AN INPUT IS CONFIGURED TO MONITOR A NEGATIVE VOLTAGE, VLx WILL TRIGGER AN UNDERVOLTAGE CONDITION.

Figure 22. VLx Positive Voltage Monitoring Timing Diagram

08170-025

#### **UV AND OV RISE AND FALL TIMES**

The  $\overline{UV}$  and  $\overline{OV}$  output rise times (from 10% to 90%) can be approximated using the following formula:

$$t_R \approx 2.2(R_{PULL-UP})(C_{LOAD})$$

where:

$R_{\text{PULL-UP}}$  is the internal weak pull-up resistance with an approximate value of 400 k $\Omega$  at room temperature with  $V_{\text{CC}}$  > 1 V.  $C_{\text{LOAD}}$  is the external load capacitance on the output pin.

When a fault occurs, the  $\overline{UV}$  or  $\overline{OV}$  output fall time can be expressed as

$$t_F \approx 2.2(R_{PULL-DOWN})(C_{LOAD})$$

where  $R_{\text{PULL-DOWN}}$  is the internal pull-down resistance, which is approximately 50  $\Omega.$  Assuming a load capacitance of 150 pF, the fall time is 16.5 ns.

#### UV/OV OUTPUT CHARACTERISTICS

Both the  $\overline{OV}$  and  $\overline{UV}$  outputs have a strong pull-down to ground and a weak internal pull-up to  $V_{CC}$ . This permits the pins to behave as open-drain outputs. When the rise time on the pin is not critical, the weak pull-up removes the requirement for an external pull-up resistor. The open-drain configuration allows for wire-OR'ing of outputs, which is particularly useful when more than one signal needs to pull down on the output.

At  $V_{\rm CC}$  = 1 V, a maximum  $V_{\rm OL}$  = 0.15 V at  $\overline{UV}$  is guaranteed. At  $V_{\rm CC}$  = 1 V, the weak pull-up current on  $\overline{OV}$  is almost turned on. Consequently, if the state and pull-up strength of the  $\overline{OV}$  pin are important at very low  $V_{\rm CC}$  an external pull-up resistor of no more than 100 k $\Omega$  is advised. By adding an external pull-up resistor, the pull-up strength on the  $\overline{OV}$  pin is greater. Therefore, if it is connected in a wire-ORèd configuration, the pull-down strength of any single device must account for this additional pull-up strength.

#### **GLITCH IMMUNITY**

The ADM2914 is immune to short transients that may occur on the monitored voltage rails. The device contains internal filtering circuitry that provides immunity to fast transient glitches. Figure 9 illustrates glitch immunity performance by showing the maximum transient duration without causing a reset pulse. Glitch immunity makes the ADM2914 suitable for use in noisy environments.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

The ADM2914 has an undervoltage lockout circuit that monitors the voltage on the  $V_{\rm CC}$  pin. When the voltage on  $V_{\rm CC}$  drops below 1.9 V (minimum), the circuit is activated. The  $\overline{UV}$  output is asserted and the  $\overline{OV}$  output is cleared and not allowed to assert. When  $V_{\rm CC}$  recovers,  $\overline{UV}$  exhibits the same timing characteristics as if an undervoltage condition had occurred on the inputs.

#### **SHUNT REGULATOR**

The ADM2914 is powered via the  $V_{\rm CC}$  pin. The  $V_{\rm CC}$  pin can be directly connected to a voltage rail of up to 6 V. In this mode, the supply current of the device does not exceed 100  $\mu A.$  An internal shunt regulator allows the ADM2914 to operate at higher input voltage levels by placing a shunt resistor in series between the supply rail and the  $V_{\rm CC}$  pin to limit the input current to less than 10 mA. Use Figure 7 in the Typical Performance Characteristics section to assist in determining the value of this resistance. Choose an appropriate location on the curve to accommodate variations in  $V_{\rm CC}$  due to changes in current through the dropper resistor.

#### **OV LATCH (ADM2914-1)**

If an overvoltage condition occurs when the  $\overline{LATCH}$  pin is pulled low, the  $\overline{OV}$  pin latches low. Pulling  $\overline{LATCH}$  high clears the latch. If an  $\overline{OV}$  condition clears while  $\overline{LATCH}$  is high, the latch is bypassed and the  $\overline{OV}$  pin behaves in the same way as the  $\overline{UV}$  pin, with an identical timeout period. If the  $\overline{LATCH}$  pin is pulled low while the timeout period is active, the  $\overline{OV}$  pin latches low, as in normal operation.

#### **DISABLE (ADM2914-2)**

Pulling the DIS pin high disables both the  $\overline{UV}$  and  $\overline{OV}$  outputs, and forces both outputs to remain weakly pulled high, regardless of any faults that are detected at the inputs. If a UVLO condition is detected, the  $\overline{UV}$  output is asserted and pulls low; however, the timeout function is bypassed. As soon as the UVLO condition clears, the  $\overline{UV}$  output pulls high. To guarantee normal operation when the pin is left unconnected, DIS has a weak 2  $\mu$ A internal pull-down current.

# TYPICAL APPLICATIONS

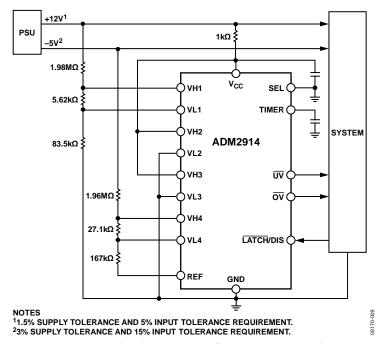

Figure 23. Typical Application Diagram for Monitoring 5 V, 3.3 V, 2.5 V, and 1.8 V

Figure 24. Typical Application Diagram for Monitoring  $+12\,V$  and  $-5\,V$

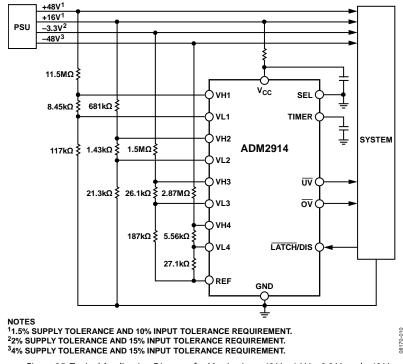

Figure 25. Typical Application Diagram for Monitoring +48 V, +16 V, -3.3 V, and -48 V

# **OUTLINE DIMENSIONS**

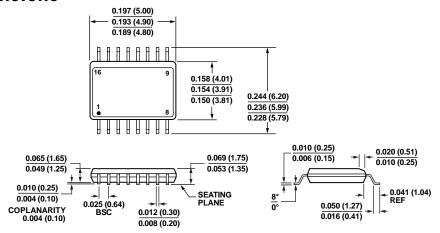

COMPLIANT TO JEDEC STANDARDS MO-137-AB

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 26. 16-Lead Shrink Small Outline Package [QSOP] (RQ-16) Dimensions shown in inches and (millimeters)

#### **ORDERING GUIDE**

| Model                          | Temperature Range | Package Description                         | Package Option |

|--------------------------------|-------------------|---------------------------------------------|----------------|

| ADM2914-1ARQZ <sup>1</sup>     | -40°C to +125°C   | 16-Lead Shrink Small Outline Package [QSOP] | RQ-16          |

| ADM2914-1ARQZ-RL7 <sup>1</sup> | -40°C to +125°C   | 16-Lead Shrink Small Outline Package [QSOP] | RQ-16          |

| ADM2914-2ARQZ <sup>1</sup>     | -40°C to +125°C   | 16-Lead Shrink Small Outline Package [QSOP] | RQ-16          |

| ADM2914-2ARQZ-RL7 <sup>1</sup> | -40°C to +125°C   | 16-Lead Shrink Small Outline Package [QSOP] | RQ-16          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

| ADM2914 |  |  |  |  |  |

|---------|--|--|--|--|--|

|---------|--|--|--|--|--|

NOTES