ОКБ "Эланор" 111024, Москва, ул. Авиамоторная, д.8А, <u>kamal.aliev@nil23.msk.ru</u>

**Реферат.** Целью данной работы была разработка модуля сбора данных, предназначенного для аналого-цифрового преобразования сигналов и передачи их на внешние устройства с целью последующей обработки и анализа. Кроме того предусмотрена возможность генерации требуемых аналоговых сигналов. Модуль сбора данных выполнен на основе современной элементной базы включающей цифровой сигнальный процессор, микросхемы АЦП, ЦАП и программируемые логические интегральные схемы (ПЛИС).

## Введение

Во многих задачах ЦОС требуется наблюдать длинные реализации аналоговых сигналов. Для этого они подвергаются аналого-цифровому преобразованию и передаются на внешние устройства обработки и анализа.

Разработанный модуль сбора данных осуществляет аналого-цифровое преобразование сигналов и их последующую передачу в реальном времени на внешние устройства для последующей обработки и анализа. Возможность генерирования требуемых аналоговых сигналов расширяет возможности модуля.

### Варианты использования разработанного модуля

На Рис 1 показана диаграмма вариантов использования модуля сбора данных. Диаграмма вариантов использования является исходным концептуальным представлением или концептуальной моделью системы [1]. Данная диаграмма показывает взаимодействие модуля сбора данных с внешними устройствами, пользователями и т.п.

Рис 1 Диаграмма вариантов использования

- Управление модулем производится с помощью внешних устройств или непосредственно пользователем

- Сбор данных, генерация сигналов осуществляется под управлением внешних устройств, либо непосредственно пользователем

- Передача собранных данных осуществляется в направление внешних устройств

- Внешняя синхронизация. Модуль сбора данных имеет возможность работы с внешним источником синхронизации

# Архитектура модуля сбора данных

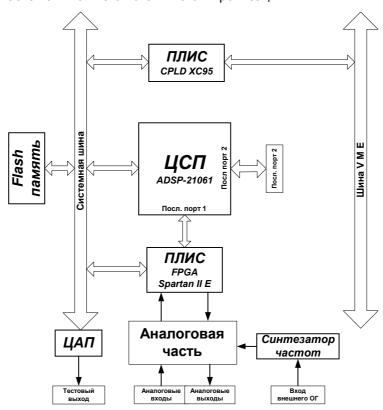

На Рис 2 показана архитектура модуля сбора данных. Разработанный модуль построен по шинной архитектуре. Модуль имеет внутреннюю системную шину и мост на внешнюю шину VME для обмена информацией с внешними устройствами. На шине VME модуль сбора данных является ведомым. Также имеет последовательный интерфейс обмена данными с внешними устройствами.

Архитектура задумана так, что чтобы поток данных с АЦП поступал на внешние устройства непрерывно в реальном масштабе времени.

Имеется возможность использование нескольких модулей сбора данных на общей внешней шине.

# Особенности реализации модуля сбора данных

Аналоговая часть модуля сбора данных имеет симметричный вход/выход и состоит из 16-битного АЦП AD9260 [2] и 14-битного ЦАП AD9764 [3] фирмы Analog Devices.

Необходимые частоты дискретизации формируются в динамически перепрограммируемом синтезаторе частот на основе петли ФАПЧ. Синтезатор частот построен на основе микросхемы ADF4001 [4] фирмы Analog Devices и TLC2933 [5] фирмы Texas Instruments. Имеется возможность работы синтезатора частот от внешнего источника синхронизации.

Рис 2 Архитектура устройства сбора данных

Программируемая логическая интегральная схема (ПЛИС) FPGA семейства Spartan IIE [6] фирмы Xilinx и цифровой сигнальный процессор (ЦСП) ADSP-21061 [7] фирмы Analog Devices обеспечивают выполнение типичных операций ЦОС (фильтрация, децимация и т.п.). FPGA также обеспечивает интерфейс обмена данными между аналоговой частью модуля и последовательным портом ЦСП. Кроме выполнения предварительной обработки сигналов, ЦСП отвечает за управление внутри модуля сбора данных.

Общение с внешними устройствами в разработанном модуле происходит по VME интерфейсу. ПЛИС CPLD семейства XC95 [8] фирмы Xilinx отвечает за выполнение функций моста между системной шиной модуля и шиной VME. Данная ПЛИС также выполняет функции загрузчика FPGA.

В разработанном модуле обмен данными с внешними устройствами также возможен по последовательному порту ЦСП.

Программы для ЦСП и конфигурационная информация для FPGA хранятся во FLASH памяти или загружаются по VME шине.

Для получения отладочной информации в УСД предусмотрен тестовый 8-битный ЦАП.

### Заключение

За счет высокой скорости выполнения типовых операций ЦОС программируемые интегральные схемы повышают общую производительность системы. Применение современных микросхем АЦП И ЦАП, динамически перепрограммируемого синтезатора частот, а также наличие двух интерфейсов обмена данными делает разработанный модуль мощным прикладным инструментом во многих задачах ЦОС. Возможность динамического перепрограммирования ПЛИС и ЦСП обеспечивает гибкость и универсальность всего устройства в целом.

Модуль выполнен в виде шестислойной печатной платы, имеющей стандартный типоразмер Eurocard 6U  $(9.184'' \times 6.299'')$  и построен на современной элементной базе с применением микросхем фирм Analog Devices и Xilinx. Данная разработка имеет применение во многих задачах сбора и обработки цифровой информации.

## Литература

- 1. А. Леоненко, Самоучитель UML, СПб.: БХВ-Петербург, 2001

- 2. AD9260 High Speed Oversampling CMOS ADC with 16-bit resolution at 2.5 MHz output word rate, Product Datasheet, Analog Devices inc, Rev. B, 2000,http://www.analog.com/productSelection/pdf/AD9260 b.pdf

- 3. AD9764 14-bit, 125 MSPS, TxDAC® D/A converter, Product Datasheet, Analog Devicesinc., Rev. B, 1999, http://www.analog.com/productSelection/pdf/AD9764 b.pdf

- 4. ADF4001 200 MHz Clock Generator PLL, Product Datasheet Rev.0, Analog Devices inc., 2001 <a href="http://www.analog.com/productSelection/pdf/ADF4001">http://www.analog.com/productSelection/pdf/ADF4001</a> 0.pdf

- 5. TLC2933 High Performance Phase-Locked Loop, Product Datasheet, Texas Instruments, January 1996

http://www-s.ti.com/sc/ds/tlc2933.pdf

6. Spartan IIE 1.8V FPGA Family, Product Datasheet, Xilinx inc.,

http://direct.xilinx.com/bvdocs/publications/ds077 1.pdf

7.ADSP-21061, Product Datasheet, Rev.B, Analog Devices inc., 2000,

http://www.analog.com/productSelection/pdf/ADSP-21061 L b.pdf

8. XC9500 In-System Programmable CPLD Family, Product Datasheet, Ver.5.0,Xilinx inc.,1999 http://direct.xilinx.com/bydocs/publications/9500.pdf

\_\_\_\_**\_**\_\_

### **DATA ACQUISITION MODULE**

Aliev K.

OKB "Elanor" 111024, Moscow, Aviamotornaya 8A, E-mail: <a href="mailto:kamal.aliev@nil23.msk.ru">kamal.aliev@nil23.msk.ru</a>

**Abstract.** The main goal of this project was to develop Data Acquisition Module. This module intends for data acquisition, data processing and signal generation and was designed using high precision ADC and DAC, DSP, FPGA and CPLD.

### Introduction

In many Digital Signal Processing (DSP) development applications it is necessary to sample analog signals with great accuracy and store a great number of sampled data for future analyzing and measurement purposes. Often many developers face one problem: how and where to store this sampled data.

Data Acquisition Module solves the problem described above and also provides some signal preprocessing and generation analog user specified signals.

### **Brief overview**

Data Acquisition Module is a 6U form factor VME card that can simultaneously provide sampling and generating analog signals. Sampled data can be transferred to external data storage devices for post-processing purposes. Module also supports serial data exchange interface.

Bridge between internal system bus and VME bus is implemented in CPLD.

SHARC DSP and FPGA from Spartan IIE family are responsible for signal pre-processing. SHARC DSP also manages all processes in the Data Acquisition Module.

PLL based frequency synthesizer provides different sampling frequencies for ADC and DAC on the basis of reference frequency.

External synchronization is a useful feature when it is necessary to get synchronization from external sources, e.g. A/D, D/A sampling must be done coherently with the external source.

# **Conclusions**

Typical DSP operations can be implemented in FPGA with great performance resulting in system performance improvement.

Data Acquisition Module was implemented on ADC, DAC, DSP and FPGA/CPLD IC's from Analog Devices and Xilinx. This module will be a useful tool in many DSP applications.