**Designed to Help You Boost Your Analog Design Power**

| NOTES: |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

#### **Table of Contents**

| Welcome to Apex               | 585 | The packages                         | 650 |

|-------------------------------|-----|--------------------------------------|-----|

| Where we live                 | 586 | Linear basics                        | 651 |

| Quality at Apex               | 587 | Class C outputs                      | 652 |

| DC-DC Converters              | 588 | Class AB outputs                     | 654 |

| The packages                  | 589 | Complex construction                 | 656 |

| Linear power delivery         | 590 | Monolithic types                     | 658 |

| PWM power delivery            | 591 | Selector guides                      | 659 |

| Basic converter block         | 592 | Amplifier selection                  | 661 |

| Basic converter operation     | 593 | Electrical limitations               | 663 |

| Defining Apex converters      | 594 | Non-linear model                     | 664 |

| What's inside                 | 595 | Common non-linear cases              | 665 |

| Shorted output response       | 596 | False summing node                   | 668 |

| Ceramic capacitors            | 598 | Reading the specs                    | 669 |

| Shutdown Plus pin             | 600 | Common mode voltage                  | 670 |

| DHC 6W singles                | 601 | Op amp protection                    | 671 |

| DHC 6W duals                  | 604 | Input protection networks            | 672 |

| DB 20W family                 | 607 | Gain switching                       | 674 |

| Triplets are coming           | 610 | To invert or not with I/P protection | 676 |

| PWM Amplifiers                | 612 | Flyback diodes                       | 677 |

| The packages                  | 613 | Transient voltage protection         | 678 |

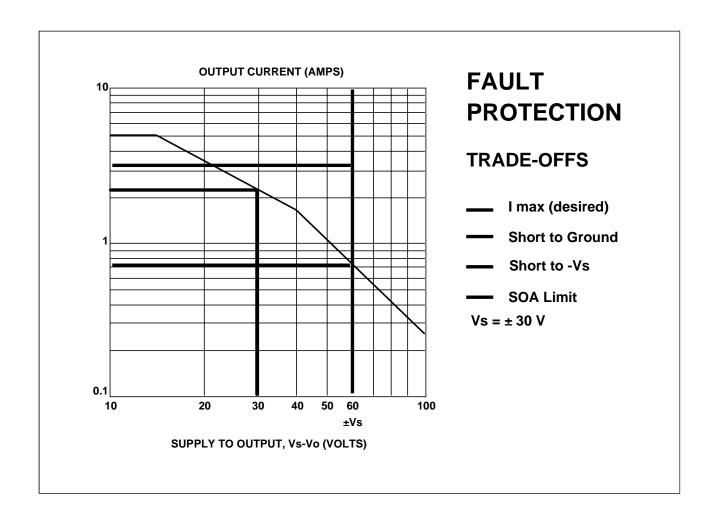

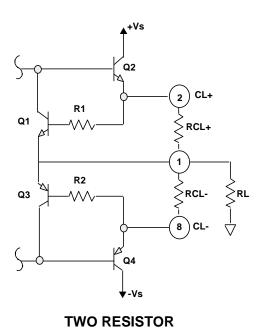

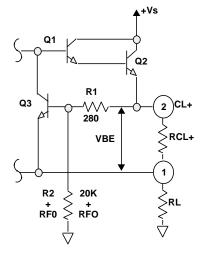

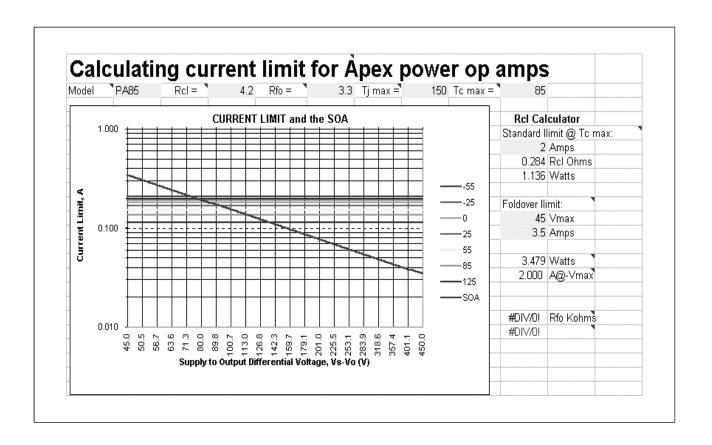

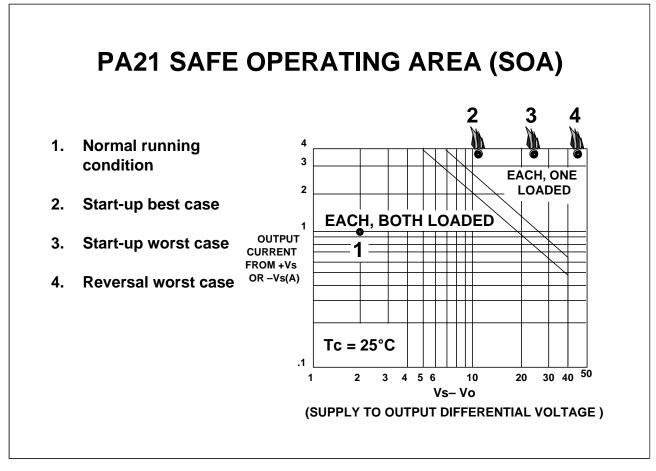

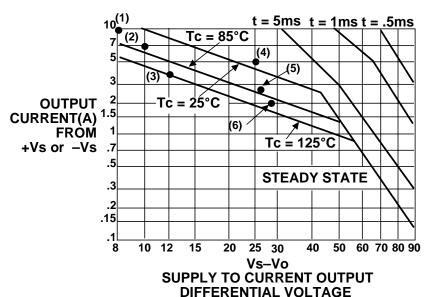

| Linear vs. PWM power delivery | 614 | SOA                                  | 679 |

| The H-Bridge                  | 617 | SOA graph                            | 680 |

| Switching concerns            | 619 | Output transistors                   | 681 |

| Evaluation kits               | 620 | Load fault to consider               | 682 |

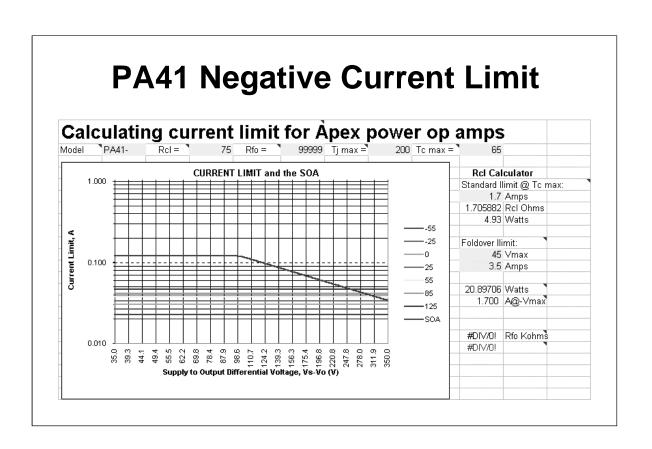

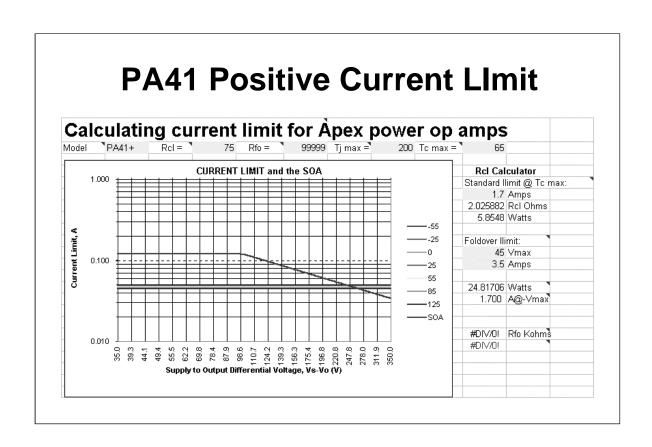

| What's inside                 | 621 | What's current limit                 | 683 |

| Block diagrams                | 622 | Thermal modeling                     | 688 |

| Transfer function             | 626 | Where to set Tj max                  | 689 |

| The integrator                | 627 | What is the internal power           | 691 |

| Samples at work               | 628 | DC vs. AC vs. reactance              | 693 |

| The frequencies involved      | 631 | Calculating the power                | 694 |

| Filter design                 | 632 | When to sweep the frequency          | 700 |

| Response with real parts      | 636 | Thermal capacity & averaging         | 701 |

| Filter termination required   | 637 | Proper mounting or not               | 702 |

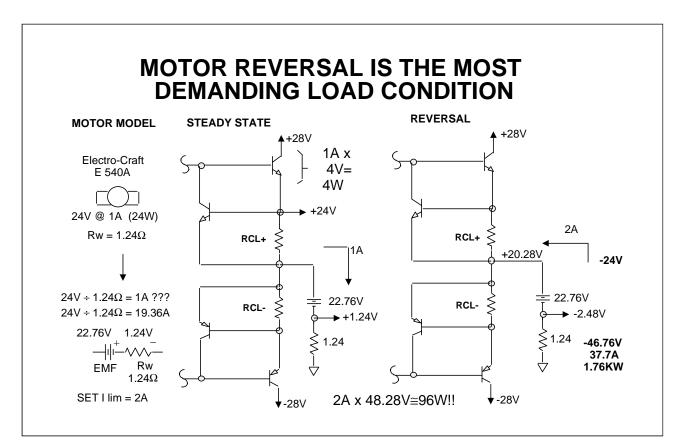

| What is -3db                  | 638 | Motor reversal                       | 705 |

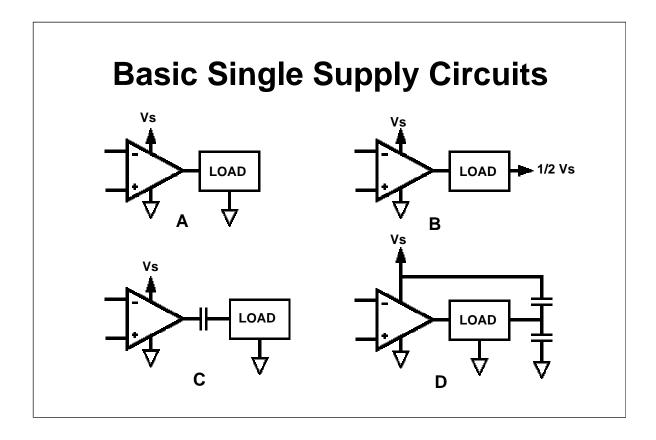

| Matching networks             | 640 | Single Supply Operation              | 706 |

| Half bridges                  | 643 | Internal limitations                 | 707 |

| Heatsinking PWMs              | 644 | Basic techniques                     | 708 |

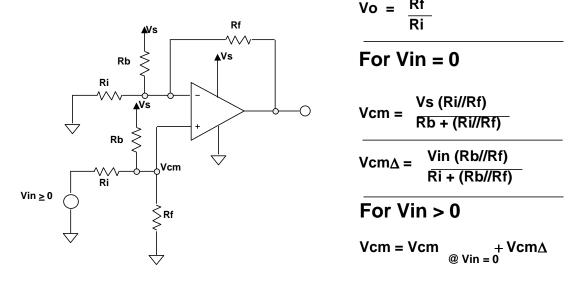

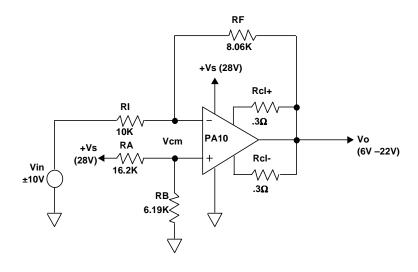

| Selector guide                | 648 | Taking care of CMV                   | 709 |

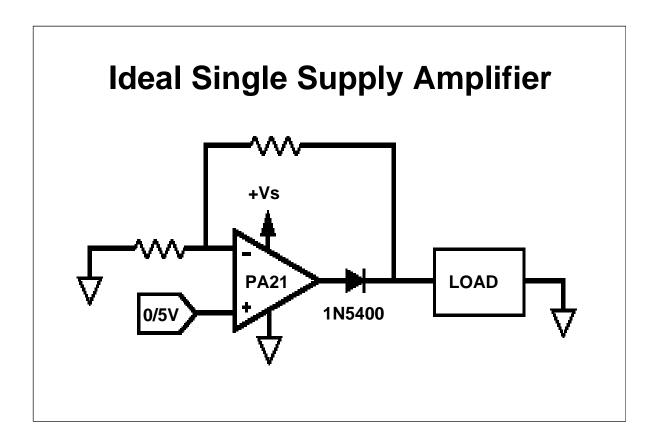

| The Apex Linear World         | 649 | PA21 is ideal                        | 712 |

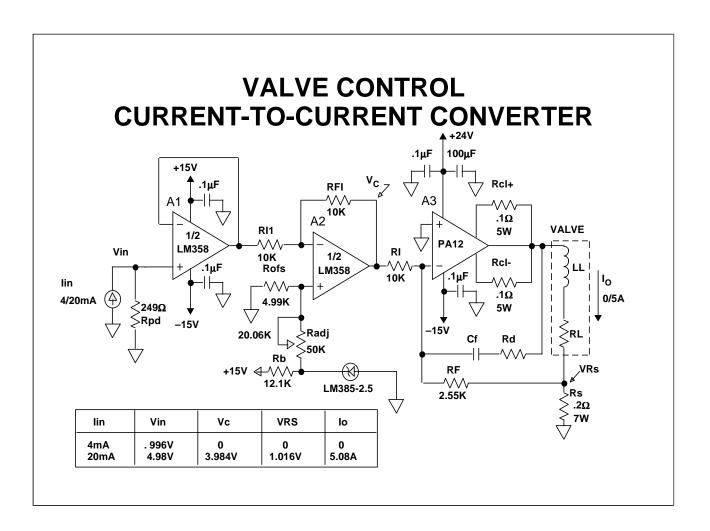

| PA21 protection alternatives    | 713 | Valve control                    | 790 |

|---------------------------------|-----|----------------------------------|-----|

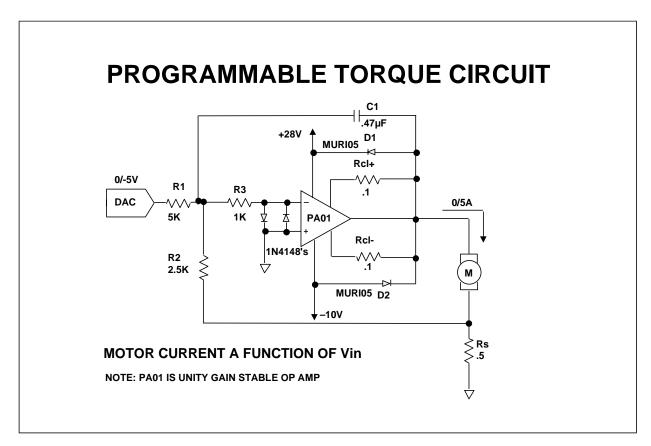

| Asymmetrical supplies           | 714 | Programmable torque drive        | 791 |

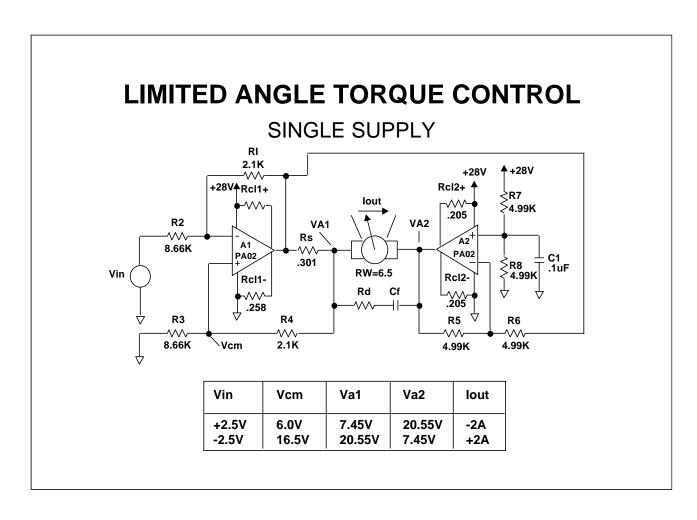

| Basic Stability                 | 715 | Howland single Vs bridge torquer | 792 |

| Eliminate coupling              | 716 | ATE                              | 793 |

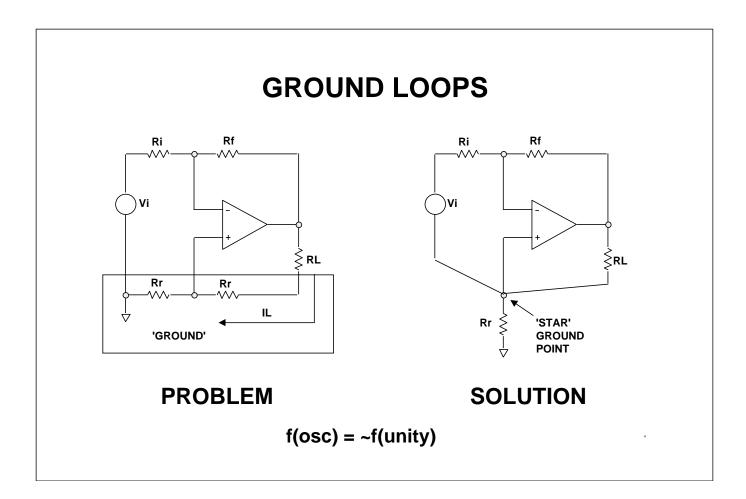

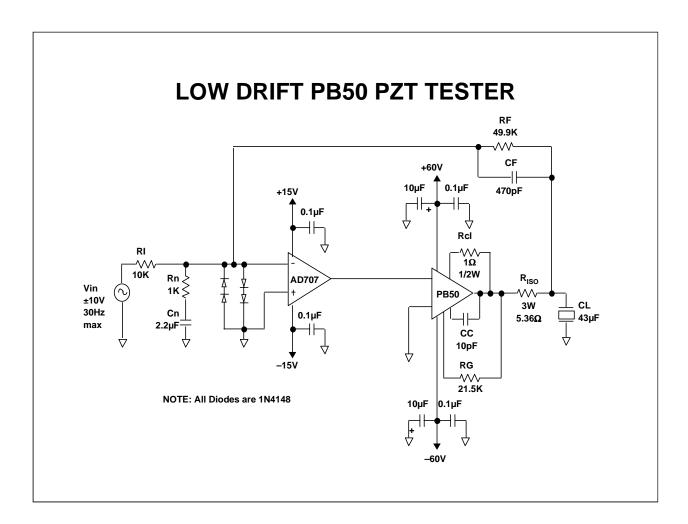

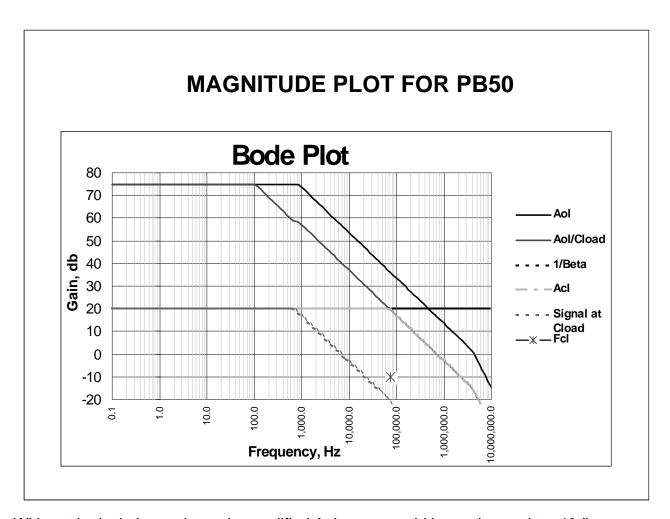

| Ground loops                    | 717 | Low drift PZT tester             | 794 |

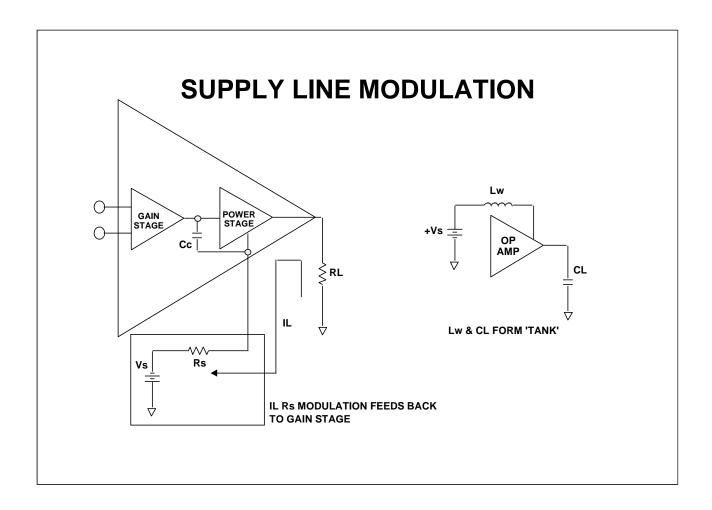

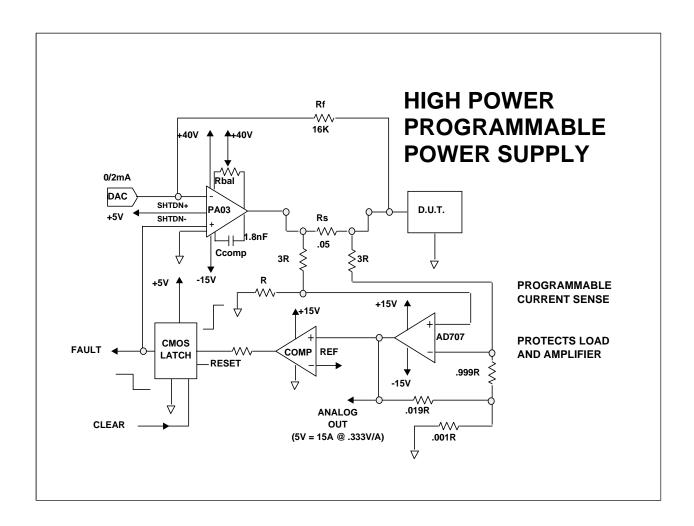

| Supply wire impedance           | 718 | Linear high power PPS            | 799 |

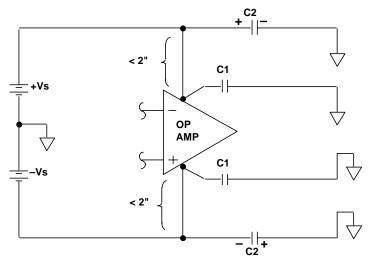

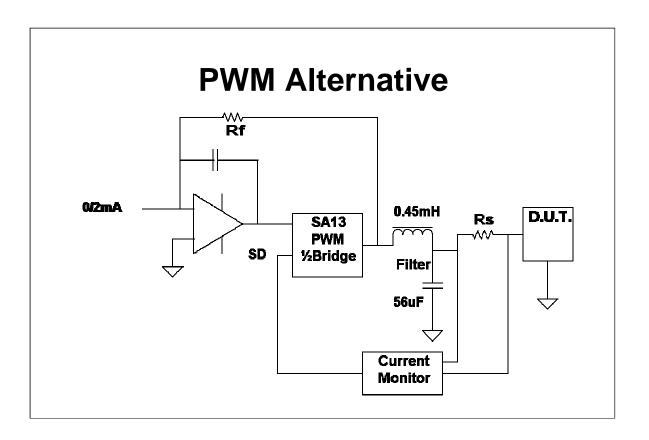

| Supply bypassing                | 719 | A PWM alternative                | 800 |

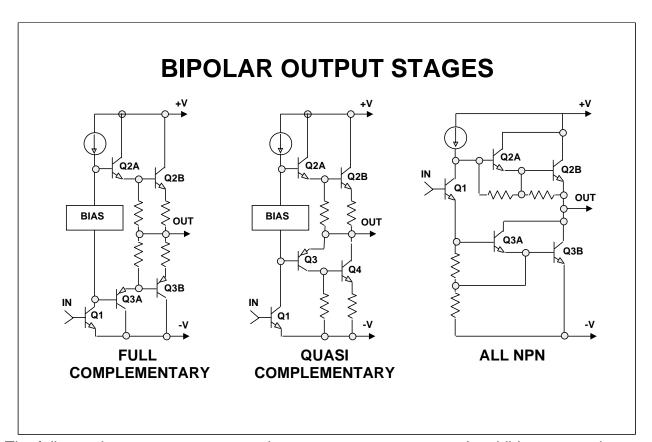

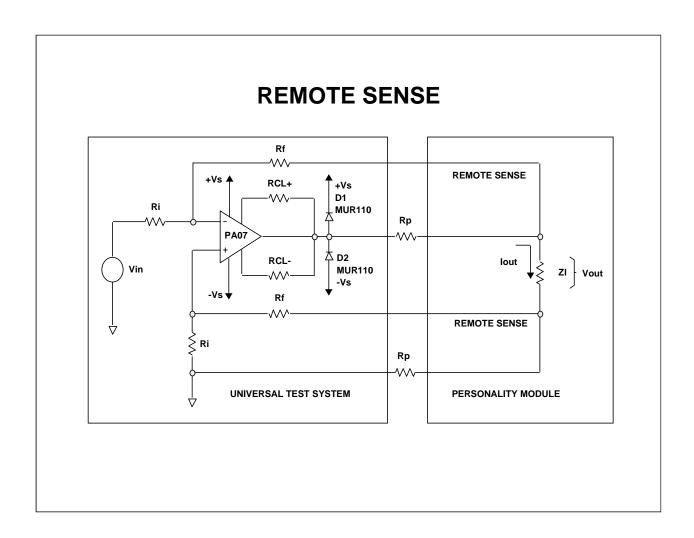

| Output stages vs. stability     | 720 | Remote sensing                   | 801 |

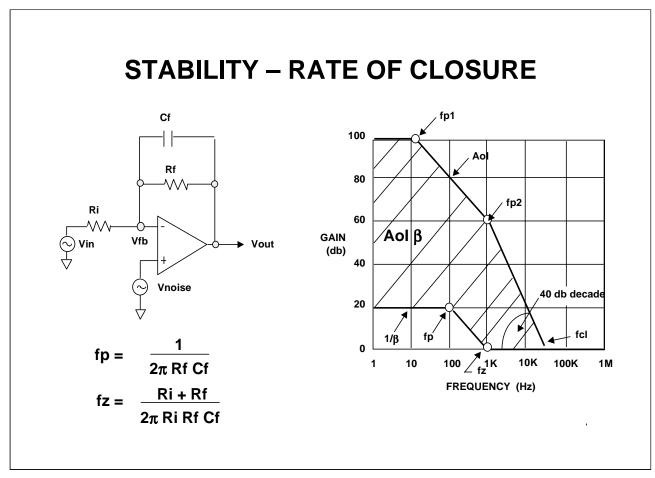

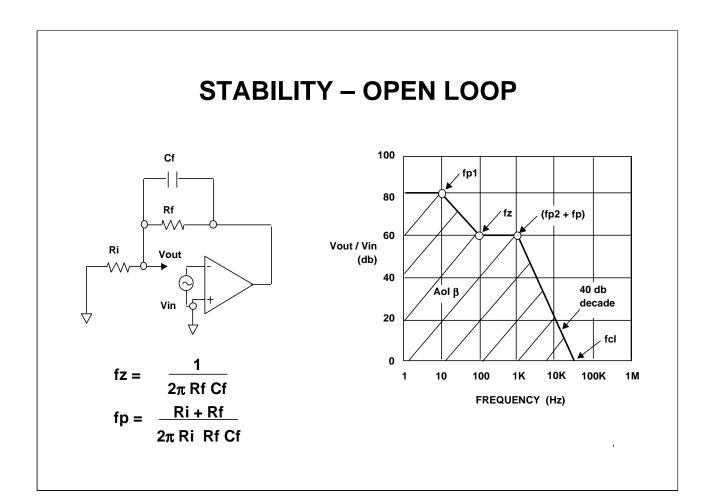

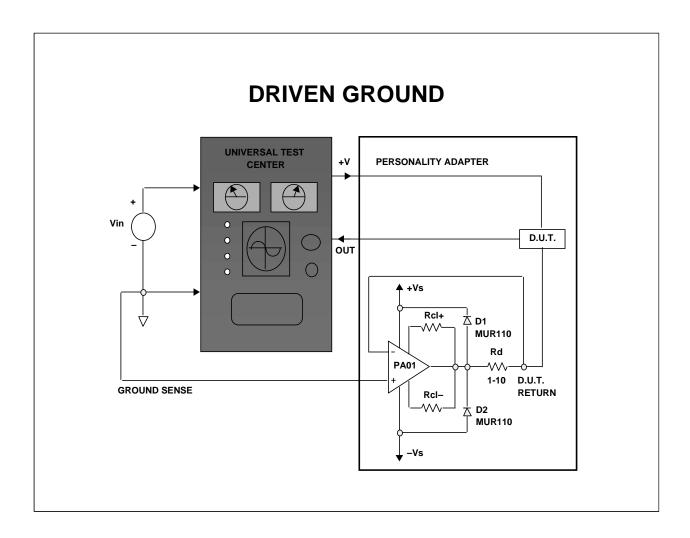

| Loop Stability                  | 722 | Driven ground                    | 802 |

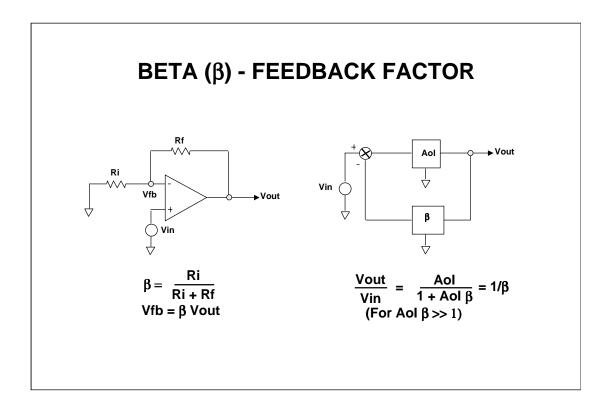

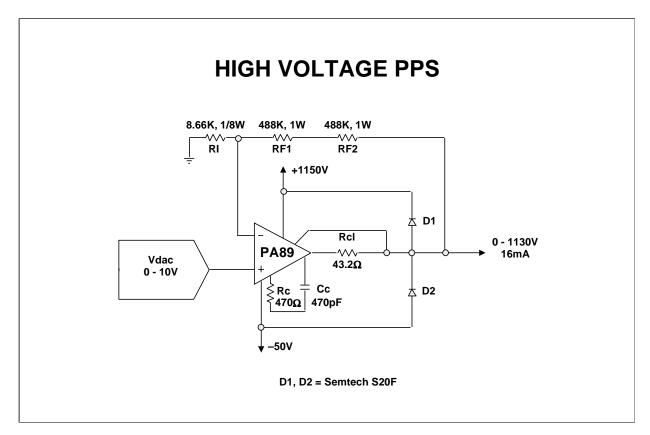

| Feedback theory                 | 723 | Very high voltage PPS            | 803 |

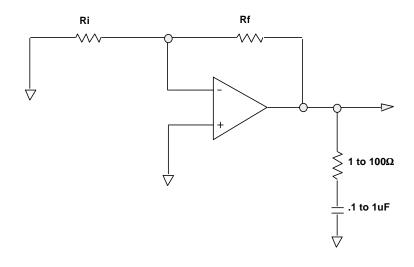

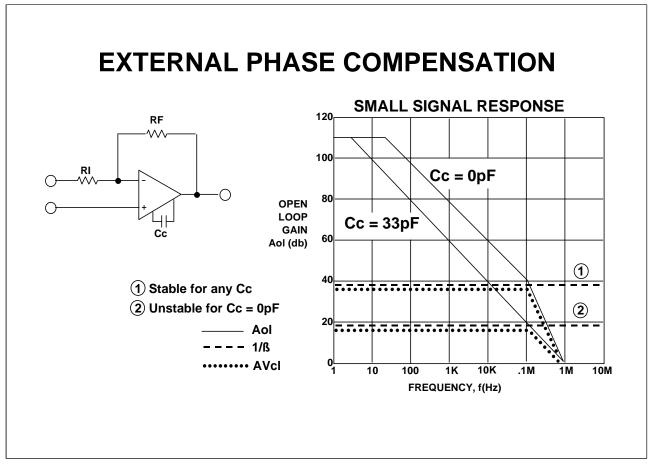

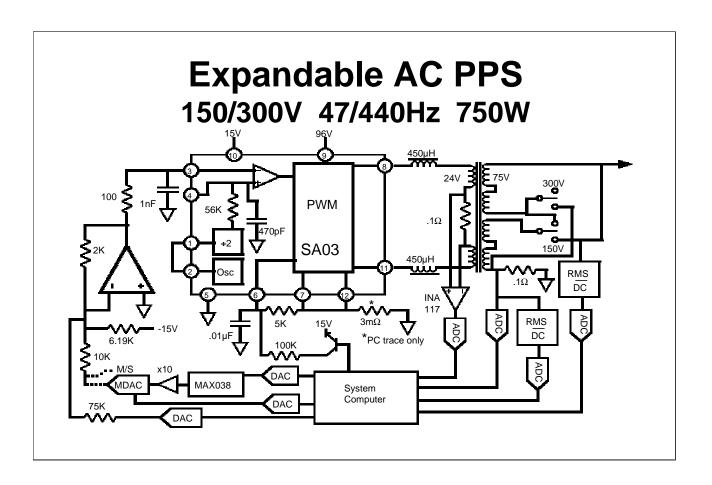

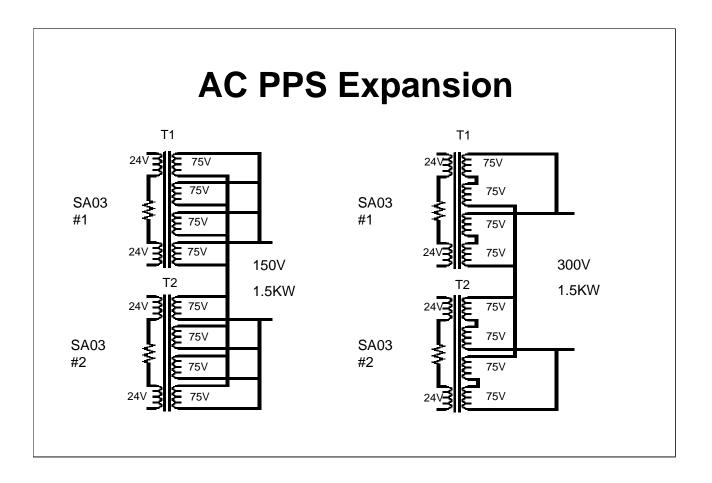

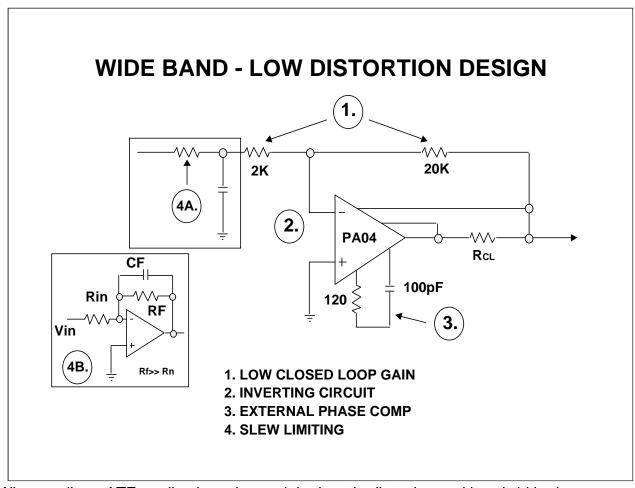

| External phase compensation     | 725 | High power AC PPS                | 804 |

| Open, closed and loop gains     | 726 | Signal Sources                   | 806 |

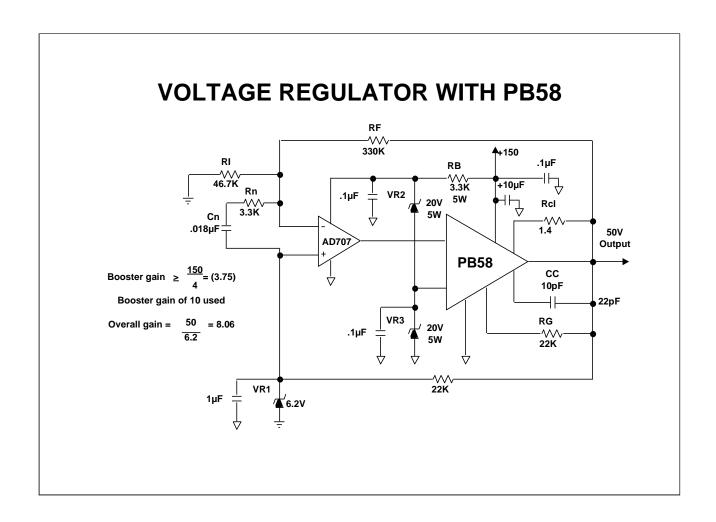

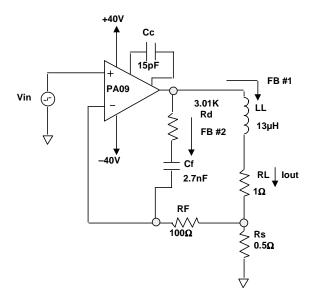

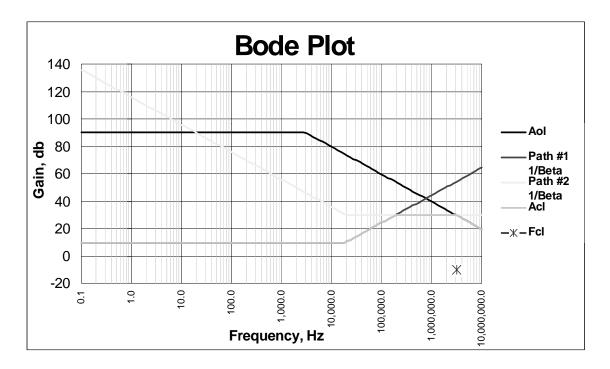

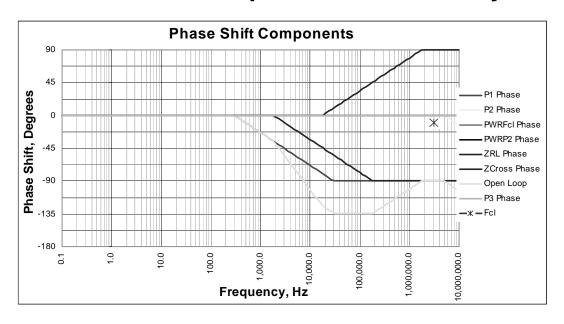

| Inductors in the feedback loop  | 728 | PB58 voltage regulator           | 807 |

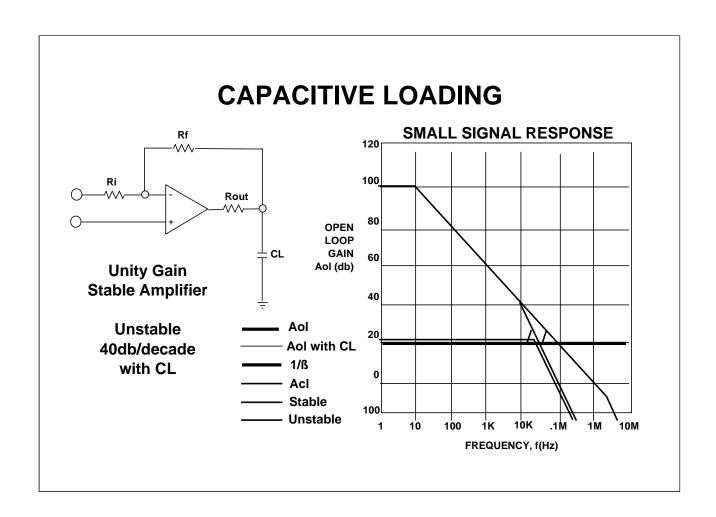

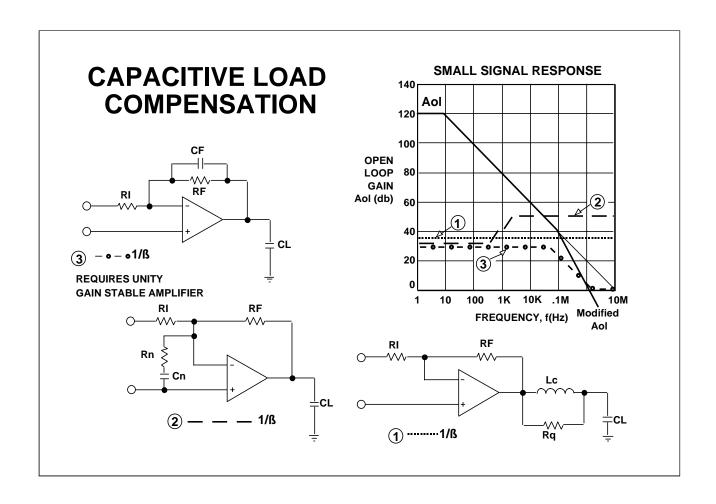

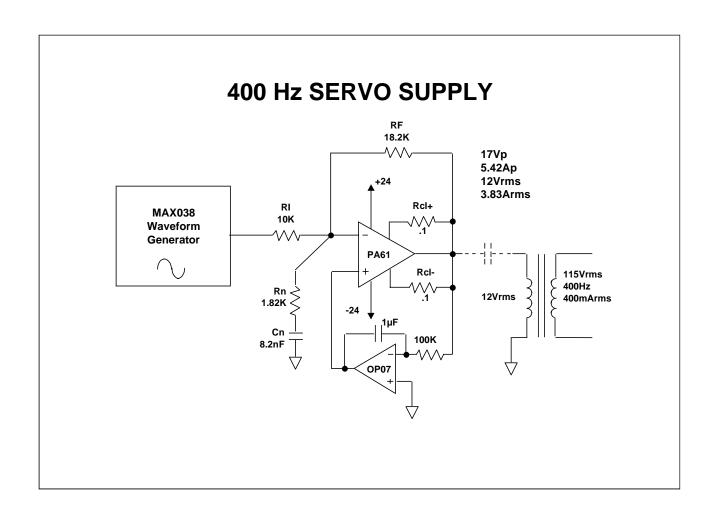

| Capacitive loading              | 734 | 400Hz servo supply               | 811 |

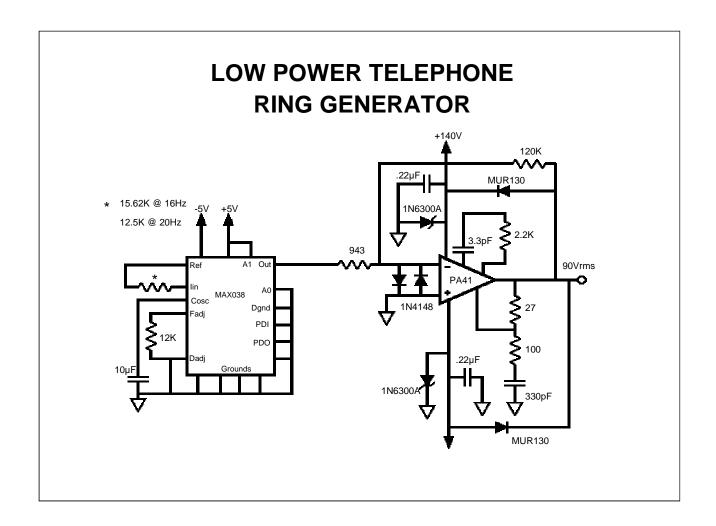

| Stability Testing               | 746 | Low power telephone ringer       | 812 |

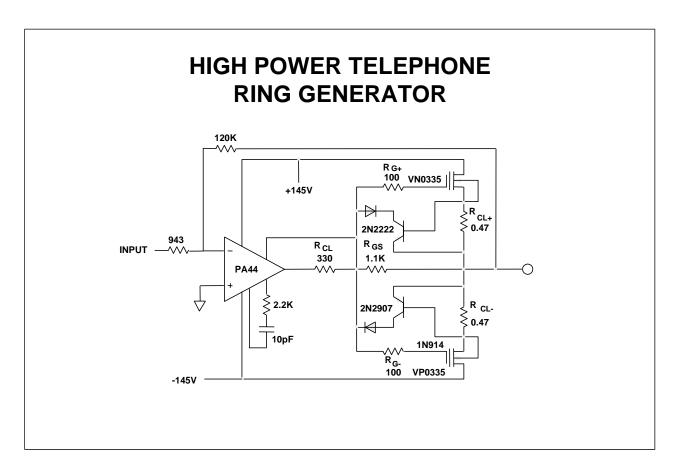

| Ringing test                    | 747 | High power telephone ringer      | 813 |

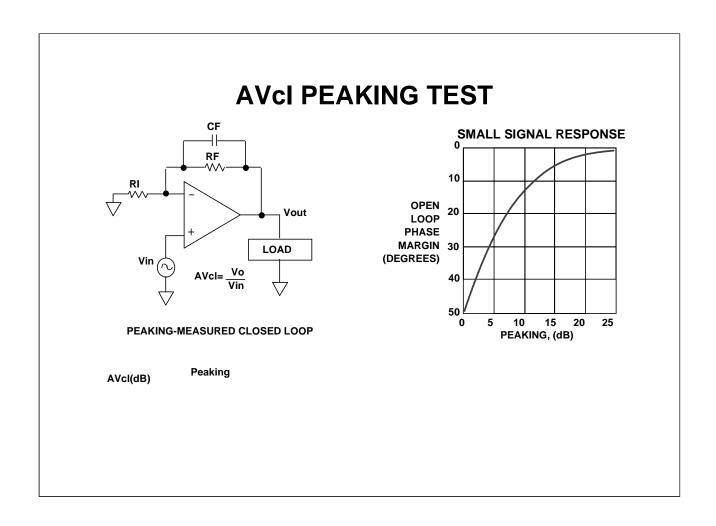

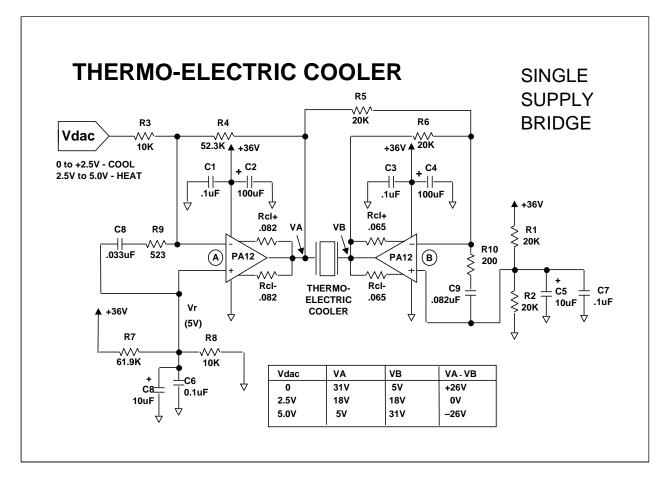

| Peaking test                    | 748 | Thermo-electric cooler           | 814 |

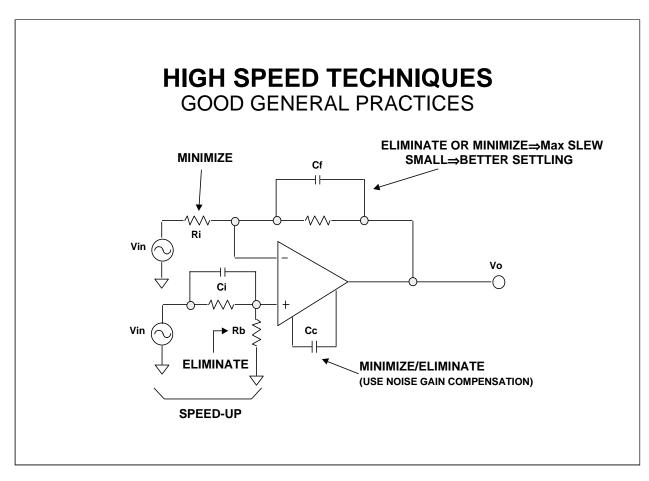

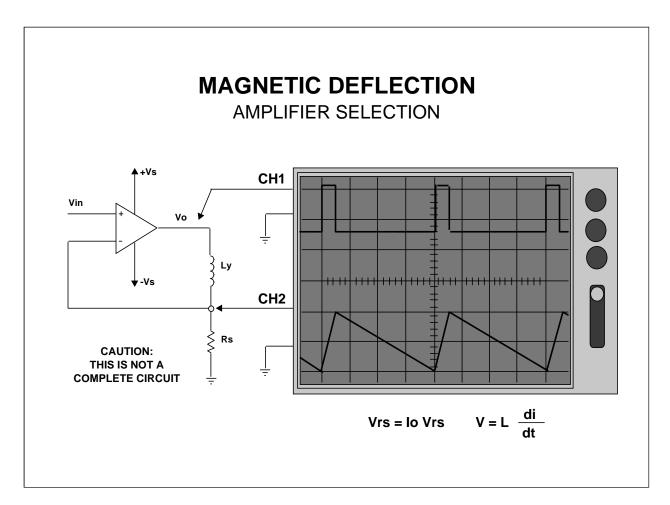

| High Speed Techniques           | 749 | Deflection                       | 815 |

| Techniques and strays           | 750 | Magnetic deflection waveforms    | 816 |

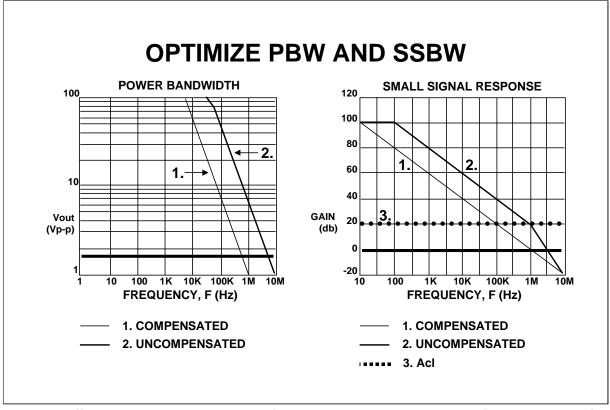

| Slew rate vs. power bandwidth   | 751 | Basic magnetic deflection        | 817 |

| Effects of compensation         | 752 | V-to-I bridge                    | 822 |

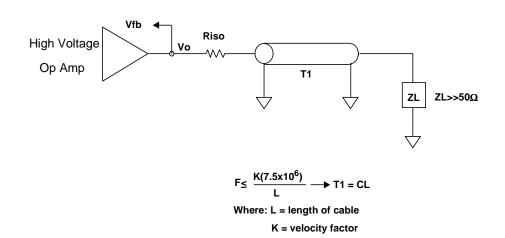

| Cable loads                     | 753 | Electrostatic deflection         | 823 |

| High Power Techniques           | 754 | Dynamic focusing                 | 824 |

| This is no laughing matter      | 755 | PZT Drive                        | 825 |

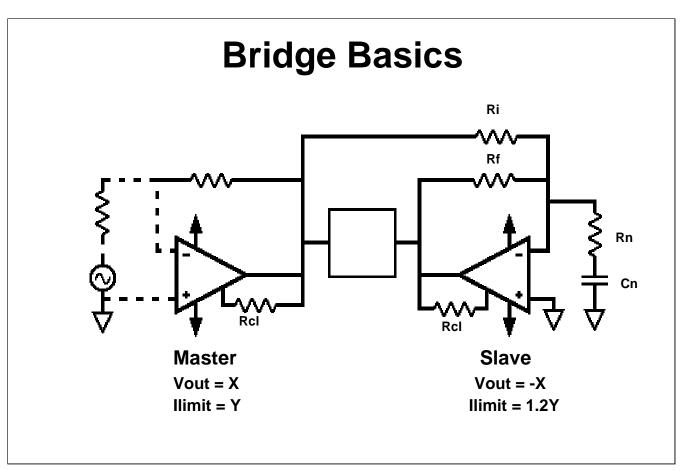

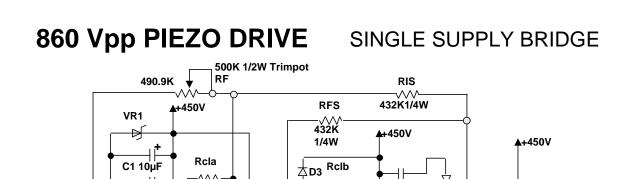

| Bridge basics                   | 757 | 860Vp-p single Vs bridge         | 826 |

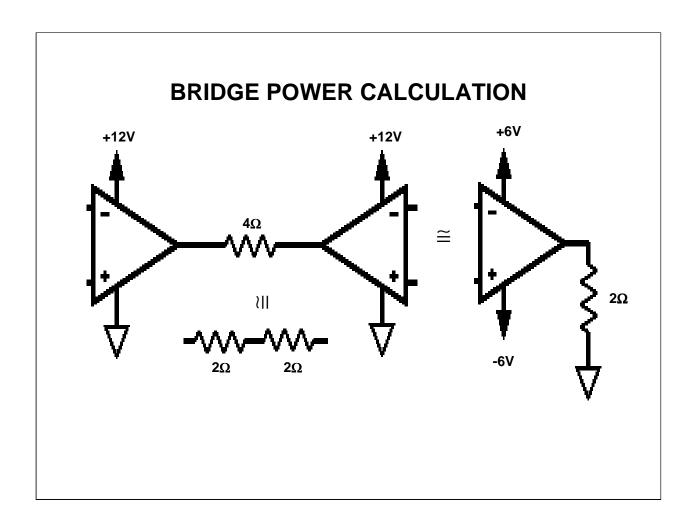

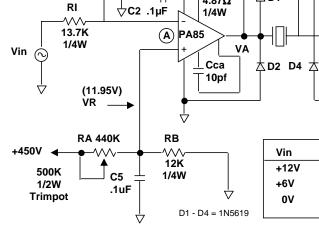

| Bridge power calculations       | 759 | ±1KV bridge                      | 827 |

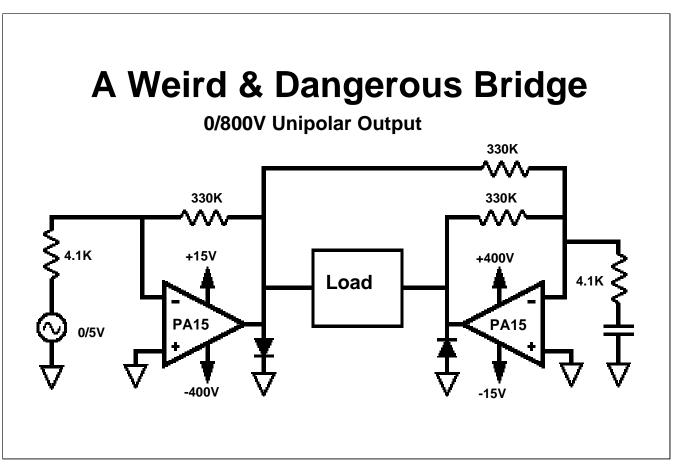

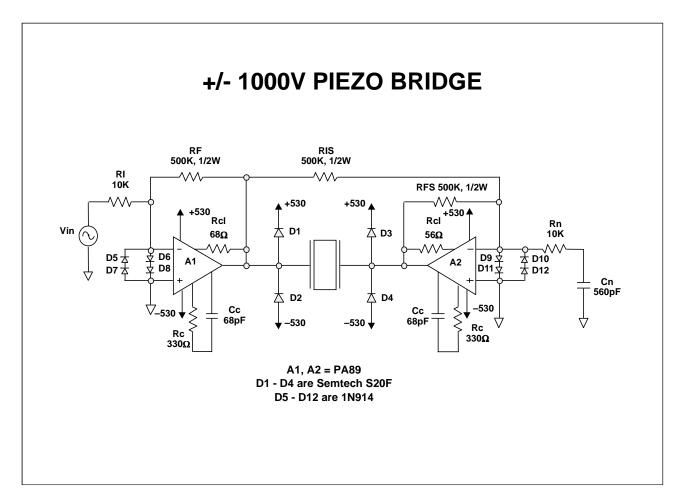

| A weird & dangerous bridge      | 760 | Composite amplifier              | 828 |

| External current buffers        | 761 | Audio/Noise Cancellation         | 837 |

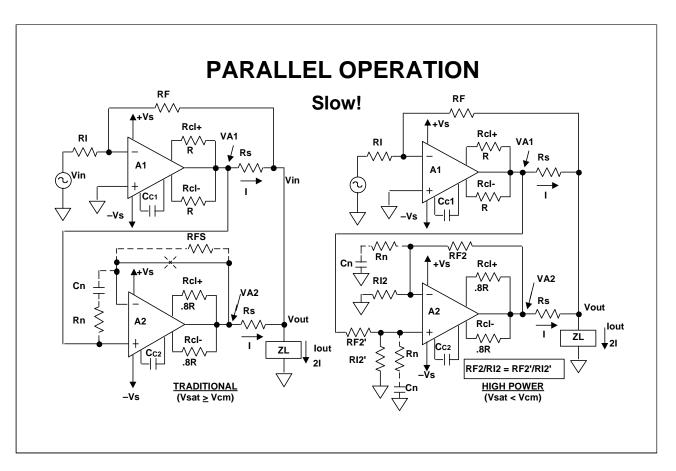

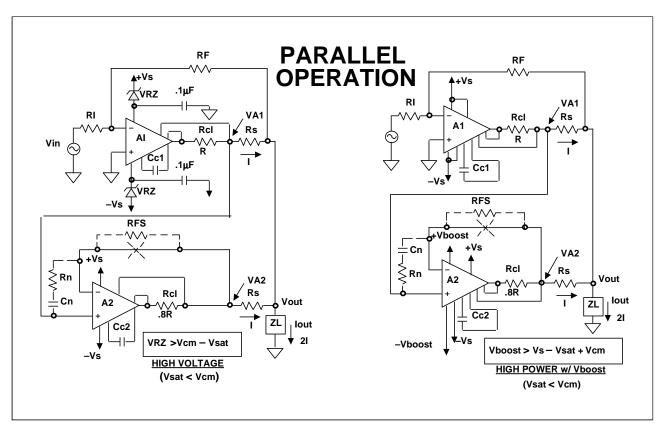

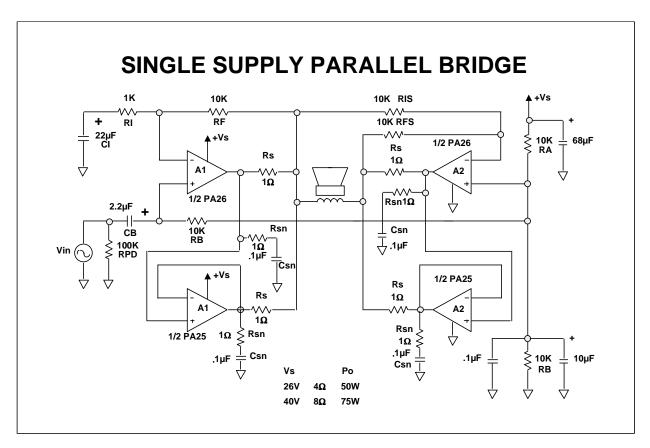

| Parallel operation              | 765 | Fast and low distortion          | 838 |

| Parallel and bridge together    | 769 | Foldover can help                | 839 |

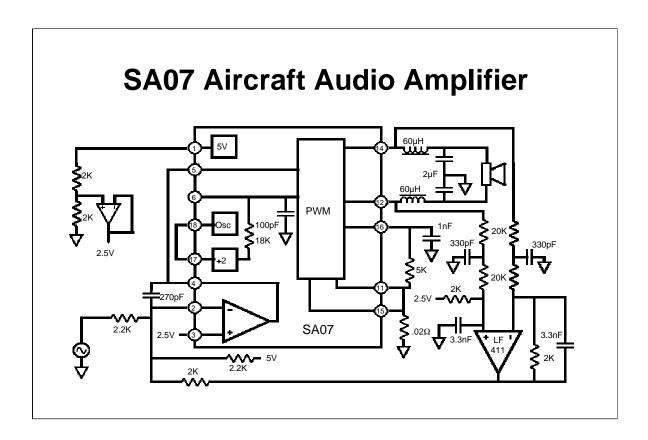

| Current Outputs                 | 770 | PWM aircraft audio               | 840 |

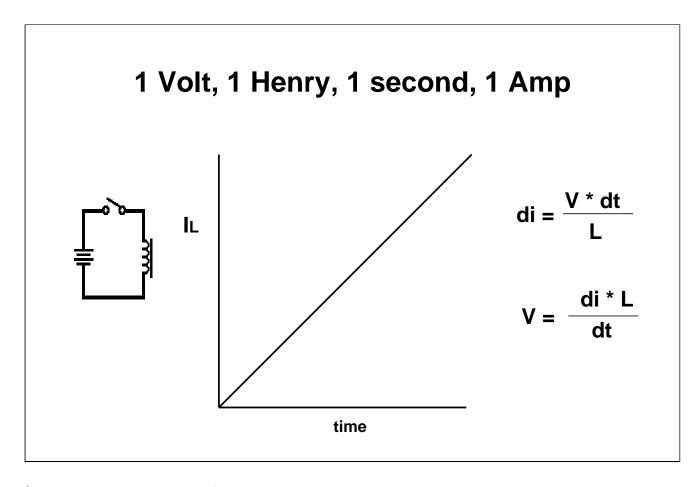

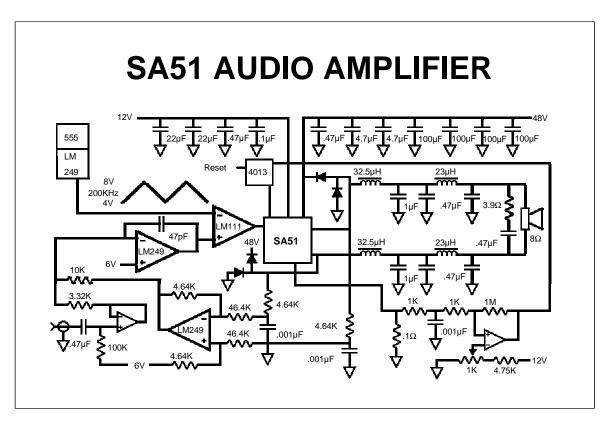

| Inductance concerns             | 771 | SA51 PWM audio                   | 841 |

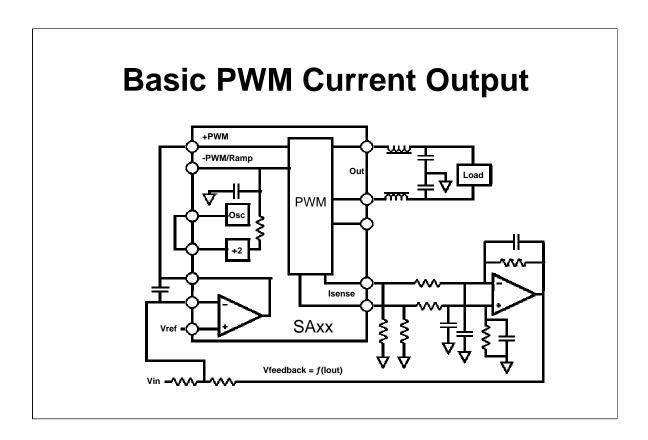

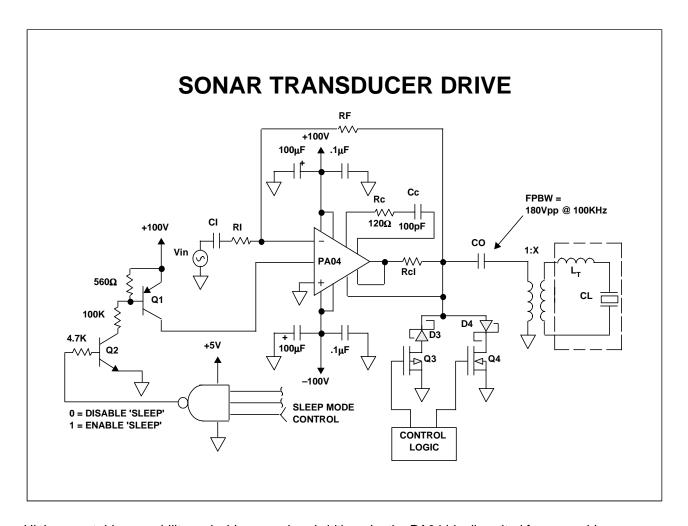

| PWM current output              | 772 | Sonar transducer                 | 842 |

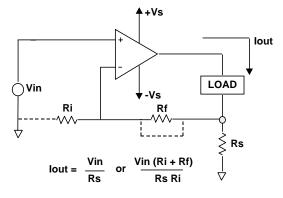

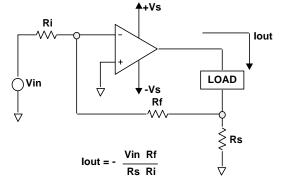

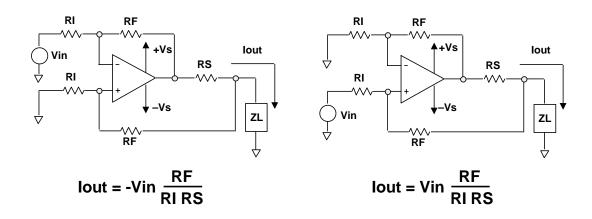

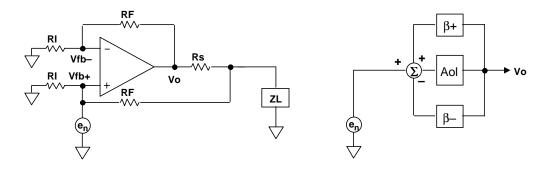

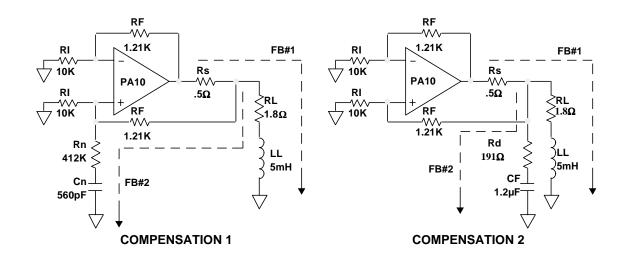

| Op amp current output           | 773 | Tools for you                    | 843 |

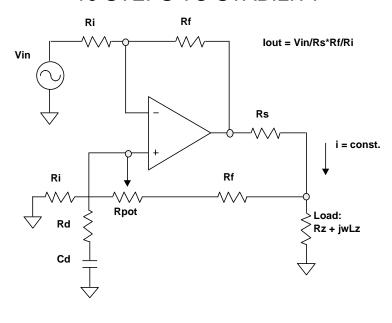

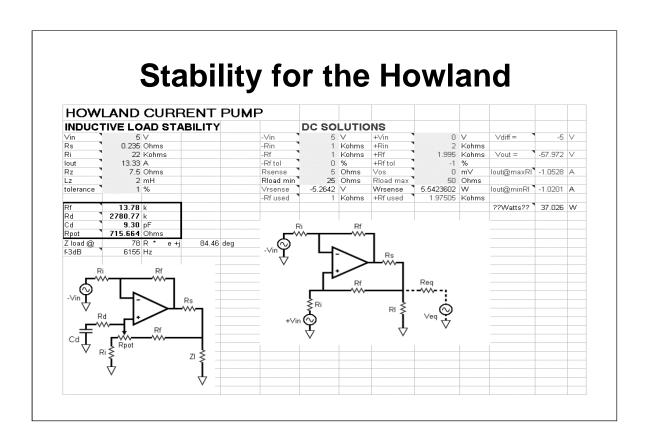

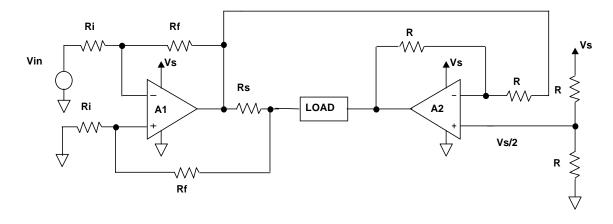

| Howland for grounded loads      | 774 | Beat the discrete                | 844 |

| Motion Control                  | 781 | Top of the line is on line       | 845 |

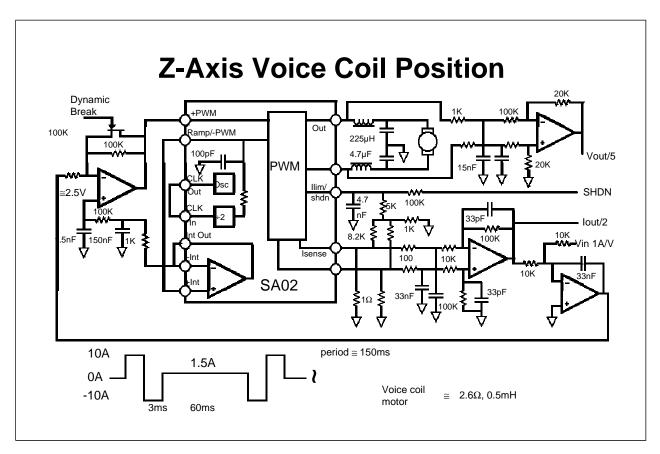

| Z-axis position                 | 782 |                                  |     |

| Brush motor specifications      | 783 |                                  |     |

| Fitting the op amp to the motor | 784 |                                  |     |

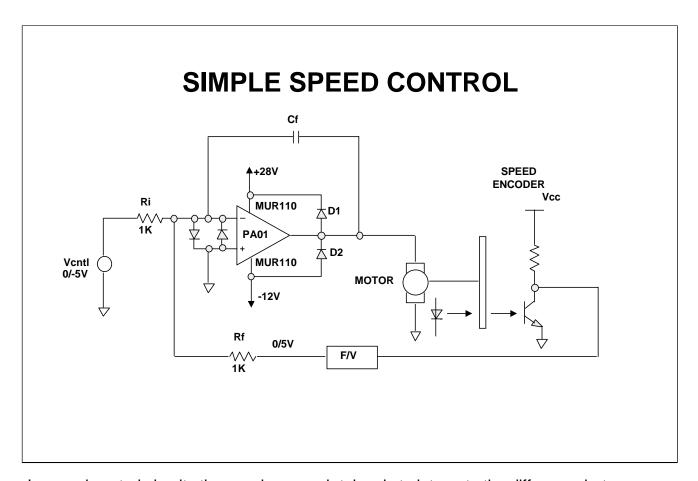

| Simple speed control            | 788 |                                  |     |

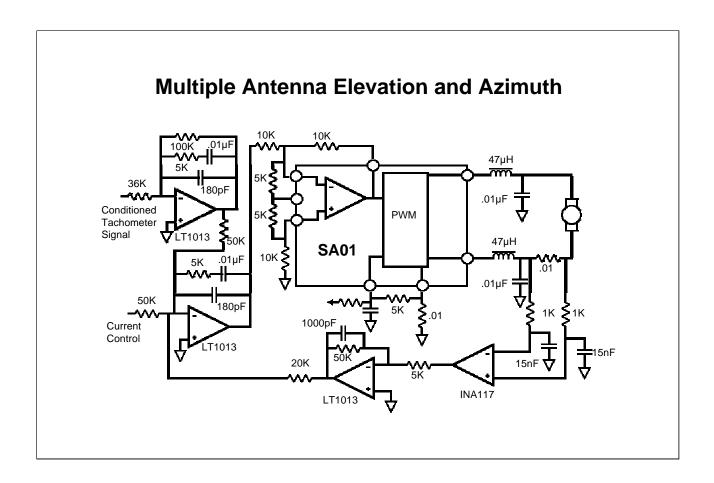

| PWM antenna position            | 789 |                                  |     |

#### **APEX MICROTECHNOLOGY CORPORATION**

DC-DC Converters ¤ PWM Amplifiers ¤ Power Op Amps

**Power Integrated Circuits with Technical Support**

Since 1981, Apex has been designing and manufacturing hybrid (chip and wire) power amplifiers. Careful attention to process development and control has made Apex the world leader in hybrid power. The products consistently perform per the data sheet. The product line now boasts the highest current, the highest voltage and highest wattage hybrids to be found anywhere in the industry.

The expertise in handling large power levels electrically and thermally has been adapted to high reliability DC-DC converters. Unique construction techniques make these converters especially impervious to demanding environmental conditions. The Apex design philosophy provides converters with no de-rating over their entire operating temperature range.

Pulse Width Modulation (PWM) amplifiers share the same reliability as their linear counterparts but utilize switching technology to greatly extend the delivered power range while keeping wasted heat in the same area as the linears.

The present Apex facility is 55,000 sq. ft. on ten acres zoned such that we can double our size. Current sales are about \$14M and we can do \$25M in this building. Almost half the area and third the cost of the building are clean room related. This class 100,000 clean room keeps the ICs clean.

Apex extends an invitation to you all to visit us and take a tour of our home to see first hand how we design and manufacture the world's best power integrated circuits.

- Total Quality Management

- Certified Mil-Std-1772 in 1989

- Certified ISO9001 in 1994

Sigma Plus has led to consistent increases in quality and performance for Apex and our customers. Sigma Plus, our Total Quality Management program, continues to produce measurable quality improvements, a culture based on teamwork, and increased value for our customers.

In alignment with *Sigma Plus*, we have instituted training and development in the fundamentals or our business, further supporting Apex teams with the tools they need to perform at high productivity and quality levels. With a firm foundation of *Sigma Plus* quality tools that solve the "how" of continuous improvement, team members are now learning the "why" with Open Book Management. As a result, Apex teams are gaining greater understanding of their personal impact on organizational systems and how they can directly improve organizational performance. By giving team members a stake in the outcome, they gain personal satisfaction and ownership of the products and services they provide to you, our customers.

We will continue to improve our systems and processes to exceed our customers' expectations. Feedback systems that identify internal and external customers' needs and expectations keep Team Apex focused on customer value. Team members have increased their job skills and have become functionally cross-trained to quickly adapt to changes that anticipate customer needs.

# **DC-DC Converters**

**Transform**

Isolate

Regulate

As you can see, these welded all steel packages are *rugged*. This is the first indicator that these converters are no ordinary breed. They are designed from top to bottom to give reliable performance in the most demanding environments.

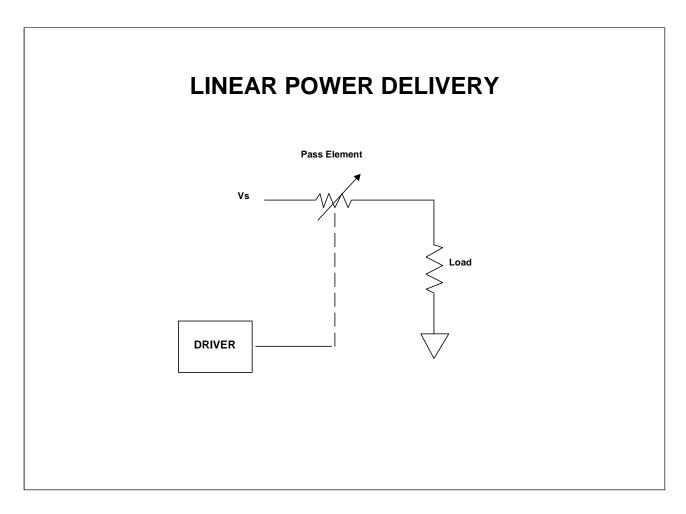

#### LINEAR POWER DELIVERY

The most popular DC-DC converter application vividly demonstrates why the DC-DC converter is the only reasonable choice compared to a linear regulator. This function is providing 5V for logic or computer circuits from a 28V bus.

Let us assume the load requires 1A @ 5V or 5W. A linear regulator would pass the 1A while having 23V across it, thus wasting 23W. With an input power of 28W, efficiency is less than 18%! Unless the application also just happens to need a 23W heater, you pay twice; once to generate the 23W and again to get rid of it. Typical efficiencies of these DC-DC converters reduce this waste heat by better than an order of magnitude.

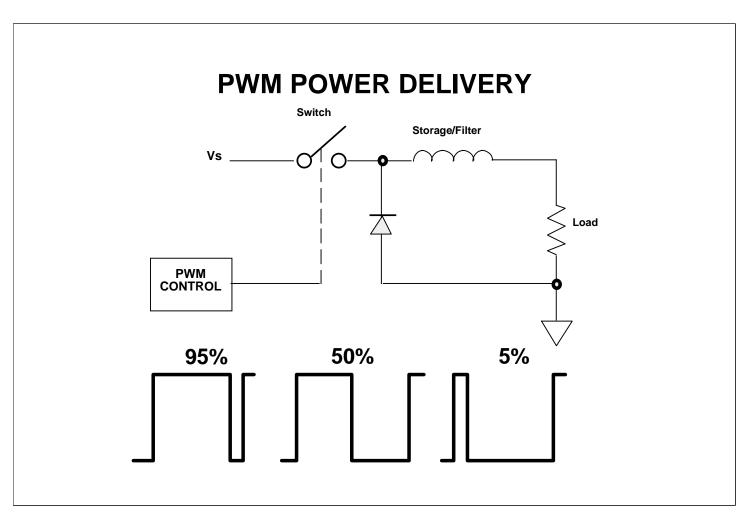

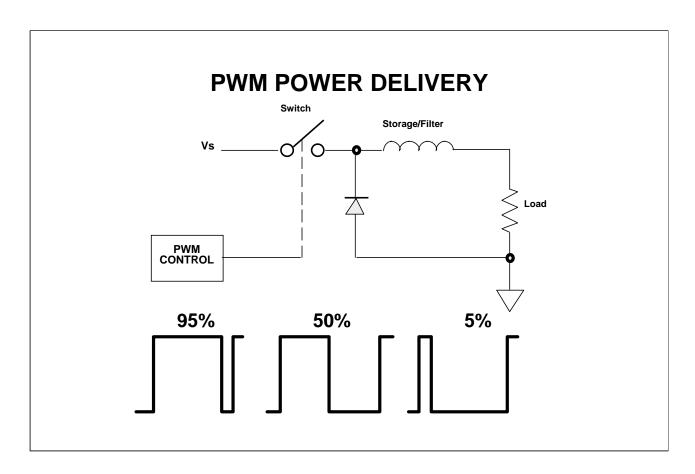

These figures illustrate the most basic pwm operation. The PWM control block converts the DC input into a variable duty cycle switched drive signal. If high output is commanded, the switch is held on most of the period. When the switch is on, losses are simply a factor of the on resistance of the switch plus the inductor resistance. As less output is commanded the duty cycle or percent of on time is reduced. When the switch is off, losses now include heat generated in the flyback diode. At most practical supply voltages this diode loss is still small because the diode conducts only a portion of the time, and voltage drop is a small fraction of the supply voltage.

The job of the inductor is both storing energy and of filtering. In this manner the load sees very little of the switching frequency, but responds to the regulator loop whose frequencies are significantly below the switching frequency.

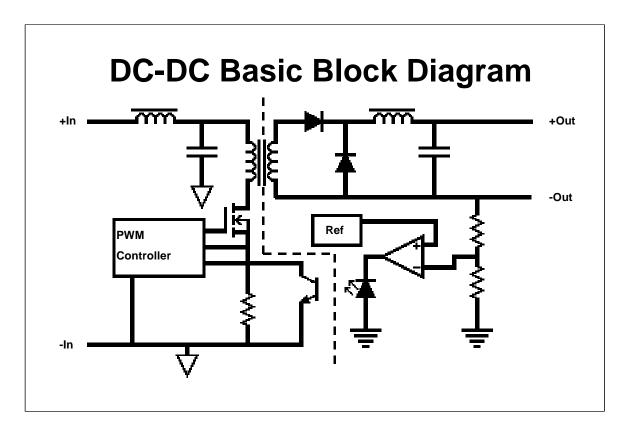

The basic blocks of the DC-DC converter consist of input and output filters, the PWM controller, a reference, an error amplifier, power isolation with rectification and error feedback isolation. The input filter reduces the effect of internal current pulses on the supply bus. Depending on the application, additional external filtering may be required. The output filter keeps most of the voltage pulses inside the converter. The need for dedicated external filter components right at the converter is unusual because there are almost always supply bypass capacitors local to the powered circuitry.

The error amplifier integrates the difference between the output voltage and the reference voltage and signals the PWM controller to lengthen the pulse if the output is low or shorten the pulse if the output is high. While this example shows optical isolation of the feedback signal, Apex also uses a time based transformer isolation technique. The optical technique requires fewer parts but great care must be taken in the design of the dynamic range to avoid saturation or starvation over temperature and operating life.

Note that this diagram uses two types of "ground" symbols, but an isolation barrier separates each type. Although cluttered, it would have been more correct to draw this diagram without ground symbols at all. Each half of this device is a floating two terminal circuit where either terminal could be "grounded" to local external circuits. It would be possible to operate on a negative input voltage or to output a negative voltage.

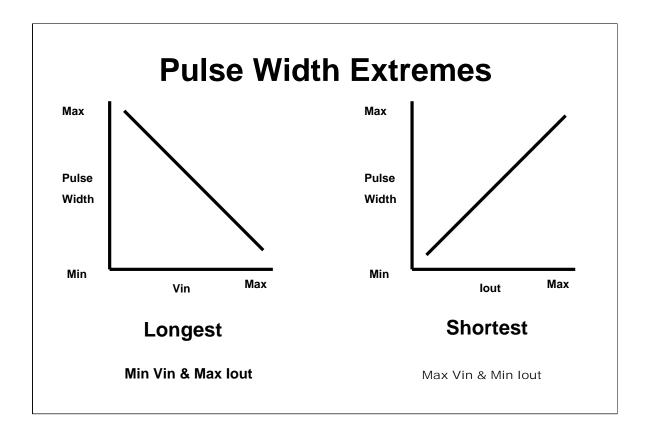

Here's the challenge of setting up the pulse width modulator: Get enough dynamic range to deliver the specified output (while maintaining regulation) even though three variables are moving over wide ranges.

If output current remains constant, the average energy into the filter inductor must remain constant. As input voltage rises, the energy delivered to the inductor in a given time increases. Inductor current is proportional to time. The controller must shorten the pulse width to close the regulation loop.

If the input voltage is constant but output current decreases, less energy must be delivered to the inductor. Again, the only variable the controller has to work with is pulse width-shorter again.

Even if input and output are rock solid, there are changes of internal losses due to temperature variations. FET on resistance, diode forward drops, copper losses, and core losses are the main factors changing over temperature. Even though some of these tend to cancel, losses typically increase a little at -55°C and increase even more at +125°C. Either case calls for increasing the pulse width to maintain regulation.

### **APEX DC-DC Converters**

- 28V input

- Hi-Rel design and construction

- No derating over specified temperature

- Fault tolerant with fault flag

- 500V isolation

- 100% temperature tested

- Programmable Vstart and remote S/D

- Hermetic packages

The classic 28V bus is usually anything but 28V. That's why the high-to-low input range of Apex converters spans 2.5:1 to over 4.5:1. Transient protection levels go even higher than that.

Some manufacturers rate the wattage of their converters based on their capability within a moderate temperature range and wait for you to ask about derating if you need to run them at higher temperatures. Not so with Apex converters: The temperature range is on the data sheet and the converter delivers full power over the entire range. And the majority of Apex models cover -55°C to +125°C!

Apex converters are not merely characterized over temperature, but are 100% temperature tested- -like a hi-rel product should be.

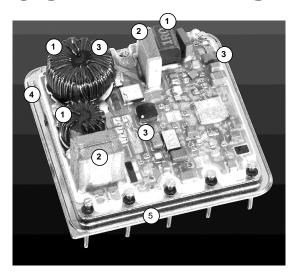

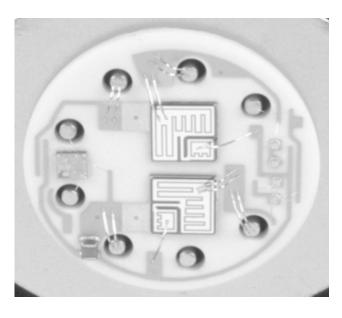

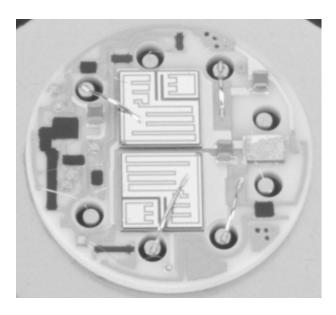

## DC/DC CONVERTERS

- 1 Surface Mount Magnetics

- (2) 100% Ceramic Capacitors

- Reflow Soldered Components

- Welded Package, Hermetically Sealed

- Low Thermal Resistance,

Ceramic on Solid Steel

#### HIGH RELIABILITY BUILT IN, APEX'S LIFETIME WARRANTY

We know our customers really put our converters to the test. That's why Apex's DHC2800 and DB2800 Series DC-DC Converters utilize all ceramic capacitors and surface mount magnetics to provide hybrid reliability across the full military temperature range and to 5000g of acceleration. The built-in ruggedness of Apex DC-DC Converters allows Apex to offer the only lifetime product warranty in the industry.

All Apex DC-DC Converter products are sold in single unit quantities to assist your circuit design evaluation. Our Evaluation Orders program even allows you to purchase up to three DC-DC Converter units and should they not meet your design needs, and they have not been damaged or soldered, you can return them to Apex within 30 days of the invoice date to receive a full credit.

#### **PRODUCT DESIGN HIGHLIGHTS**

- Commercial grade parts designed for military ruggedness

- Withstands 5000g acceleration

- 100% ceramic capacitors offer higher reliability

- DHC Series: Input meets MIL-STD-704A requirements (80V transient play through)

- DB Series: Input meets MIL-STD-704D requirements (80V transient survival)

- -55°C to +125°C full power operation

- Fault Tolerant

- Full short circuit protection

- Fully isolated

- Output voltage adjustment standard

- Remote shutdown provides on/off capabilities

#### **Upon a Shorted Output you would:**

- A. Run hot with current > 100% or

- B. Run cool with low duty cycle

With power devices, deciding what to do about the dreaded short circuit on the output is always interesting. Do you have the space and the cooling capacity to simply set a current limit safely above the required output power level and let the unit run hot? While quite rare, there are a few applications where a load fault is so unlikely that no safety provisions are required for the power stage.

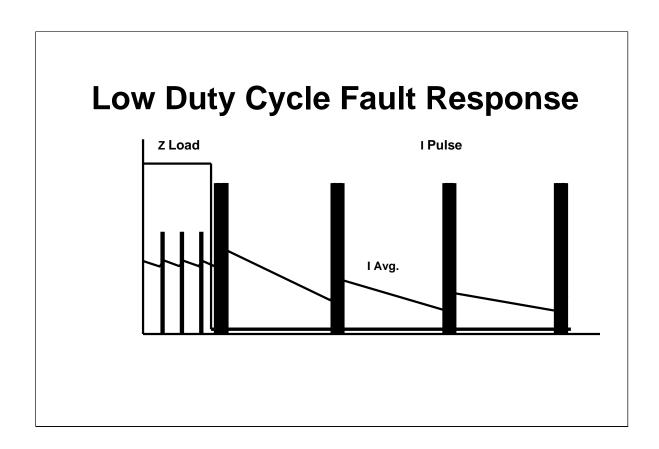

With low duty cycle fault response, Apex DC-DC converters bring a new level of confidence. Imagine watching the input current to a converter driving near full load. It's time to run the load fault test--the current meter DROPS! The first time you see this, it looks <u>wrong</u>. But it isn't wrong, its low duty cycle fault response at work.

With a normal load impedance corresponding to a near full load, we see moderate width pulses and the average current as expected for the efficiency of the converter. While it is not graphed, the error feedback signal is also at a moderate level.

When the load impedance plunges to zero or near zero, the error feedback signal swings to its maximum. It actually calls for a pulse width longer than the controller is capable of producing. The low duty cycle circuit picks up on this allowing one pulse out, but then it puts the converter to sleep for about 10 times the maximum pulse width. Even though internal heat generation during this big pulse is higher than before the fault condition, reducing the duty cycle to about 10% makes the average heat generation less than when running at full load. This low average power mode of operation is continued as long as the fault is present. Normal operation resumes when the fault is cleared.

# **CERAMIC CAPS ONLY**

- Improved hi-temp reliability

- Improved time and temperature stability

- Smaller values than tantalum/electrolytic

- Added application flexibility

Electrolytic and tantalum capacitors are known to excel at packing lots of capacitance in a small space. Like most other things in our world, there are trade-offs required. Apex designers kept high reliability as their prime design goal while making component selections.

Electrolytic and especially tantalum capacitors simply can't come close to matching the reliability performance of ceramic in the upper areas of the full military temperature range. These high density capacitors excel in temperatures suitable for habitation, but Apex converters go a lot further.

Ceramic capacitors also exhibit a lower temperature coefficient and are more stable over time. This makes temperature characterization of your circuit easier because the dynamic performance of the converter is more stable over temperature.

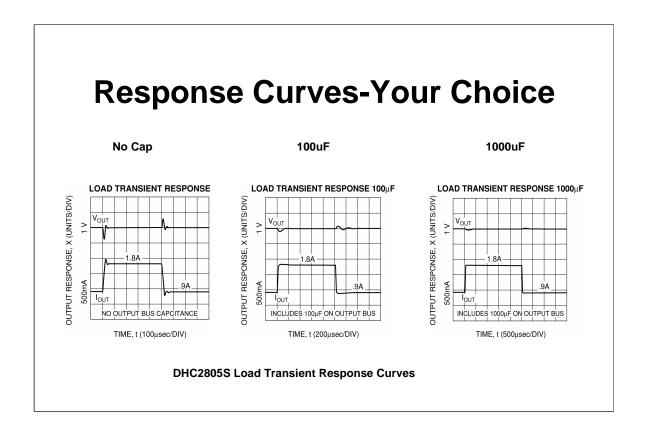

Now for the trade-off part: Ceramic capacitors can't even think of the volumetric efficiencies of electrolytic or tantalum types, so capacitor values are limited to fit in the hybrid package. It turns out though that these smaller values yield flexibility akin to an op amp featuring external compensation. Dynamic or transient performance can be tailored to fit the application.

The choice really is yours. Is your application fast and sensitive to 0.75 peak deviations from 5V? Or is it a slower system which is more sensitive to longer term 10mV deviations; maybe where the 5V is used as an analog reference?

Please note the time scale changes between the graphs. In applications where the output is used as an analog reference voltage, using no external capacitor may be the way to go. Settling time in this graph is under 100µs. Even though the peak deviation is high, a system running at 100Hz will likely never see the short transient.

For faster systems, the use of an external capacitor will greatly reduce the peak deviation, but with a settling time in the millisecond range.

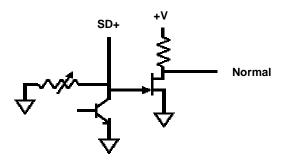

#### Shutdown+ Pin

- Shutdown with an open collector

- Program Vstart with a resistor

- Monitor faults with a J-FET

Would you like to gain some control over turn-on sequencing of your system? The Shutdown+ pin has three functions which can all be used in all combinations. The first function is that of programming a low voltage start-up point. Installing only one resistor to ground will set the level according to:

R = 210K/(Vstart-9.5)

This means with an open or several hundred Kohms, start-up is about 9.5V. The 9.5V level is increased by 210K/R, so 21Kohms yields about 19.5V start-up.

The second function is really a digital over-ride of the analog function above. Use an open collector transistor to ground the pin and the function is now a remote shutdown.

Would you like to know when something is putting your converter in a hurt? The Shutdown+ pin is also an output function: A load fault condition will cause a negative pulse on the pin from above 10V to below 1V for around 100ms for each power pulse in the low duty cycle fault response mode of operation.

| DHC2800S Series |        |      |       |

|-----------------|--------|------|-------|

| DHC2803S        | 12-50V | 5W   | 1.52A |

|                 | 13-50V | 6W   | 1.82A |

| DHC2805S        | 12-50V | 6W   | 1.2A  |

| DHC2812S        | 11-50V | 5W   | .417A |

|                 | 16-40V | 5.4W | .45A  |

| DHC2815S        | 11-50V | 5W   | .333A |

|                 | 16-40V | 5.4W | .36A  |

| DHW2805S        | 16-40V | 7.5W | 1.5A  |

This is the smallest series of converters from Apex (electrical and mechanical). They fit in an industry standard footprint with the exception that an NC pin is used to implement the Adjust/Comp function. If an existing application makes no connection to the NC pin, the DHC2800 series will drop in. These models are also available with an NC option.

The DHC2803S can be extended to 6W if minimum input is raised to 13V.

The DHW2805S is the same basic converter optimized for greater power at a reduced input voltage range.

Data as of July 1999.

## **DHC2800S Special Features**

- MHE2800/ASA2800 Compatible

- -55°C to +125°C temperature range

- Mil-Std-704 (80V survive only)

- DHC2805S plays thru 80V

- +/-10% Adjust range

- 1 inch square package

The DHC converters feature a transformer isolated feed forward topology operating at 400KHz to allow its extremely wide input voltage range.

The external connection through a resistor to the summing junction of the error amplifier can be used for voltage adjustment. These models are also offered with no connection to this pin.

#### **DHC2800D Series**

Unbal DHC2812D .333A 11-50V 5W +.208A 16-40V 5.4W ±.225A .36A +.167A 11-50V 5W .267A DHC2815D 16-40V 5.4W ±.18A .288A

Again, this is the smallest series of converters from Apex (electrical and mechanical). They fit in an industry standard footprint with the exception that an NC pin is used to implement the Adjust/Comp function. If an existing application makes no connection to the NC pin, the DHC2800 series will drop in. These models are also available with an NC option.

The current ratings labeled "±" are for balanced currents on the positive and negative sides. The "Unbal" column indicates the maximum current for a single output. The other output may then supply current bringing total delivered watts up to the converter rating. As an example the DHC2812D running on 32V can be loaded to 0.36A on one side and 0.09A on the other side. To maintain regulation, the lighter load must draw at least 20% of the total power regardless of the total watts.

## **DHC2800D Special Features**

- MHE2800/ASA2800 Compatible

- -55°C to +125°C temperature range

- Dual Tracking Regulation

- Mil-Std-704 (80V survive only)

- +/-10% Adjust range

- 1 inch square package

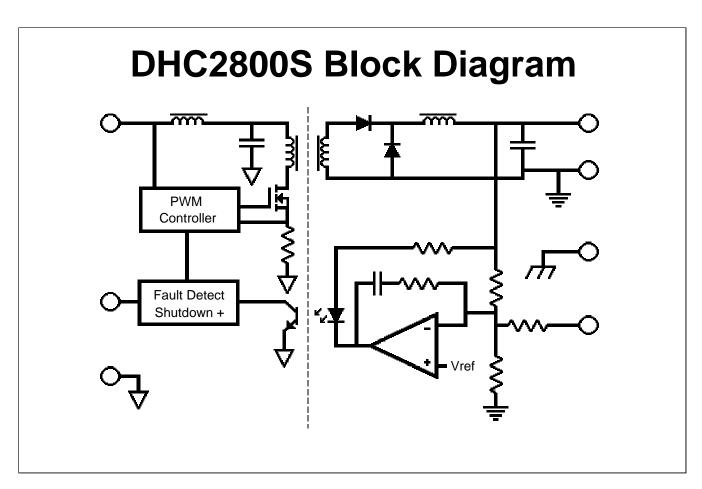

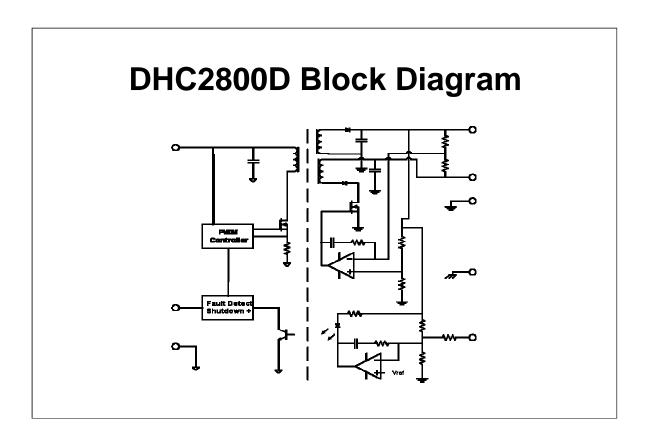

The input section of these dual converters is just like the input of the singles. On the output section, note the top transformer winding along with the lower op amp form a regulated positive output in a similar fashion to the single converter.

The lower transformer winding is the heart of the negative output. In the middle we have the unique feature of the DHC duals: the second op amp and the power MOSFET provide tracking regulation for the negative output.

| DB2800S Series |      |     |      |

|----------------|------|-----|------|

| DB2803S        | 3.3V | 18W | 5.5A |

| DB2805S        | 5V   | 20W | 4A   |

| DB2812S        | 12V  | 23W | 1.9A |

| DB2815S        | 15V  | 22W | 1.5A |

|                |      |     |      |

|                |      |     |      |

This series of converters from Apex takes a jump in electrical and mechanical size. The extremely rugged MO-127 package was developed by Apex to meet high power requirements. Total footprint area is 3 square inches and the pins are dual-in-line.

Data as of July 1999.

## **DB2800S Special Features**

- Kelvin remote sensing

- 16 to 40V Input range

- -55°C to 125°C temperature range

- Mil-Std-704D (80V survive only)

- +/-10% Adjust range

- Rugged MO-127 package

- Synchronizable-up to 3 directly

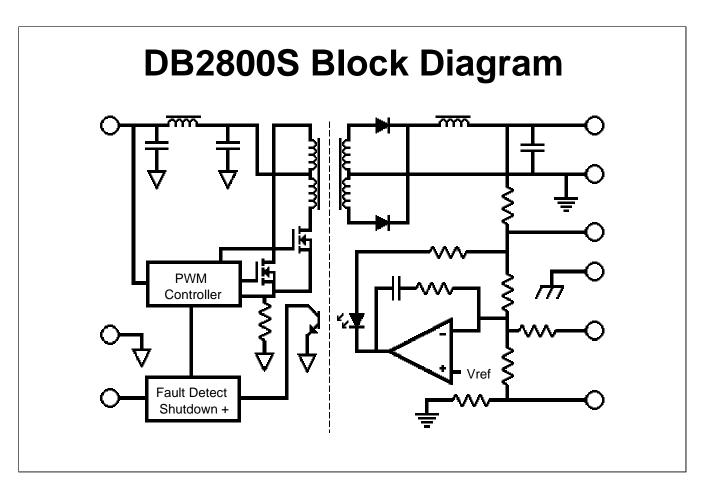

The DB converters feature a current mode push-pull topology operating at 500KHz. The larger 12 pin package allows better filtering, Kelvin sensing, synchronization and output voltage adjustment.

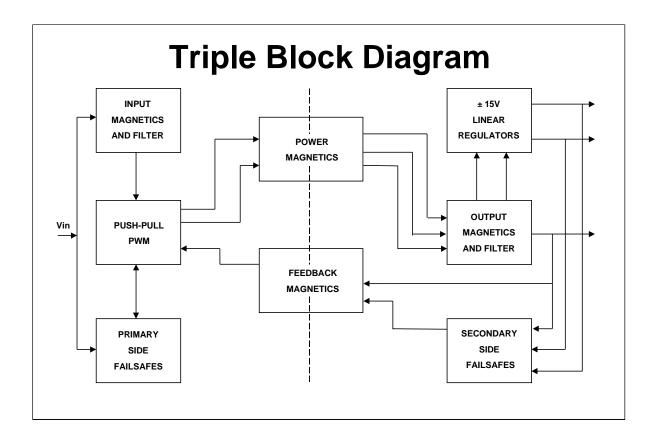

## **Coming Soon - 30W Triples**

5V 4A +/-15V .33A

5V 4A +/-12V .41A

1.35" x 2" Dual-in-line package

Dual supply outputs use linear regulators

Requires no minimum load

The number one design goal of this family of converters was SURVIVAL through any transient up to 80V, not just the converter, but for all outputs to stay within data sheet absolute maximums for logic and linear parts likely to be used with the converter.

Central to this survivability is the load fault protection circuit. Upon sensing an over current situation the converter shuts down for about 20ms. On restart, current limiting is increased about 50% for 100µseconds to help bring up heavy capacitive or difficult to handle loads. If the over current still exists after about 2ms, the cycle start over. The converter then runs about a 10% duty cycle during fault conditions eliminating overheating even at case temperatures of +125°C.

The remainder of the failsafe circuits concentrate primarily on orderly turn on and off. Whether these on-off sequences are initiated by normal power up, load faults or transients, the converter never outputs enough voltage to damage standard logic or linear parts.

## **PWM**

#### **Pulse Width Modulation**

- More Work

- Less Waste

As delivered power levels approach 200W, sometimes before then, heatsinking issues become a royal pain. PWM is a way to ease this pain.

As power levels increase the task of designing variable drives increases dramatically. While the array of linear components available with sufficient voltage and current ratings for high power drives is impressive, a project can become unmanageable when calculation of internal power dissipation reveals the extent of cooling hardware required. Often the 20A drive requires multiple 20A semiconductors mounted on massive heatsinks, usually employs noisy fans and sometimes liquid cooling is mandated.

This slide illustrates the linear approach to delivering power to the load. When maximum output is commanded, the driver reduces resistance of the pass element to a minimum. At this output level, losses in the linear circuit are relatively low. When zero output is commanded the pass element approaches infinity and losses approach zero. The disadvantage of the linear circuit appears at the midrange output levels and is often at its worst when 50% output is delivered. At this level, resistance of the pass element is equal to the load resistance which means heat generated in the amplifier is equal to the power delivered to the load! We have just found the linear circuit to have a maximum efficiency of 50% when driving resistive loads to mid-range power levels. When loads appear reactive, this efficiency drops even further.

These figures illustrate the most basic PWM operation. The PWM control block converts an analog input level into a variable duty cycle switch drive signal. If high output is commanded, the switch is held on most of the period. The switch is usually both on and off once during each cycle of the switching frequency, but many designs are capable of holding a 100% on duty cycle. In this case, losses are simply a factor of the on resistance of the switch plus the inductor resistance. As less output is commanded, the duty cycle or percent of on time is reduced. Note that losses now include heat generated in the flyback diode. At most practical supply voltages this diode loss is still small because the diode conducts only a portion of the time and voltage drop is a small fraction of the supply voltage.

The job of the inductor is both storing energy during the off portion of the cycle and of filtering. In this manner the load sees very little of the switching frequency, but responds to frequencies significantly below the switching frequency. When the load itself appears inductive, it is often capable of performing the filtering itself.

With the PWM circuit, the direct (unfiltered) amplifier output is either near the supply voltage or near zero. Continuously varying filtered output levels are achieved by changing only the duty cycle. This results in efficiency being quite constant as output power varies compared to the linear circuit. Typical efficiency of PWM circuits range from 80 to 95%.

# CONTRASTING DISCRETE LINEAR, HYBRID LINEAR AND HYBRID PWM 1KW DESIGNS

|                            | Discrete<br>Linear | Hybrid<br>Linear | Hybrid<br>PWM |

|----------------------------|--------------------|------------------|---------------|

| Wasted Heat                | 500W               | 500W             | 100W          |

| \$/Year <sup>1</sup>       | \$438              | \$438            | \$88          |

| Package Count <sup>2</sup> | 8 x TO-3           | 2 x PA03         | 1 x SA01      |

| Heatsink                   | 0.11°C/W           | 0.11°C/W         | .55°C/W       |

|                            |                    |                  |               |

Almost all power amplifiers (low duty cycle sonar amplifiers are a notable exception) must be designed to withstand worst case internal power dissipation for considerable lengths of time compared to the thermal time constants of the heat sinking hardware. This forces the design to be capable of cooling itself under worst case conditions. Conditions to be reckoned with include highest supply voltage, lowest load impedance, maximum ambient temperature, and lowest efficiency output level, and in the case of reactive loads, maximum voltage to current phase angle.

Consider a circuit delivering a peak power of 1KW. A 90% efficient PWM circuit generates 100W of wasted heat when running full output, and around 50W driving half power. The theoretically perfect linear circuit will generate 500W of wasted heat while delivering 500W. Table 1 shows three possible approaches to this type design. In all three cases it is assumed ambient temperature is +30°C and maximum case temperature is +85°C. It also assumes power ratings of the TO-3 devices to be 125W each. Heatsinks for linear designs require multiple sections mounted such that heat removed from one section does not flow to other sections.

<sup>&</sup>lt;sup>1</sup> Continuous operation at a cost of \$.10/KWH. If equipment is located in a controlled environment total cost will be considerably higher.

<sup>&</sup>lt;sup>2</sup> Package count must be doubled for the discrete design if bipolar output is required.

# Benefits Resulting From PWM Efficiency

- Operating cost savings

- Capital cost savings

- Reduced heatsinking 5:1

- Smaller, lighter finished product

# H-BRIDGE PROVIDING BIPOLAR OUTPUT FROM A SINGLE SUPPLY

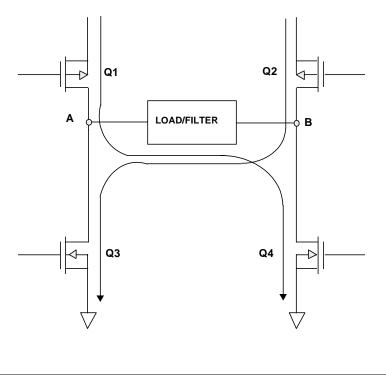

The simple form of a PWM circuit examined thus far is very similar to a number of switching power supply circuits. If the control block is optimized for producing a wide output range rather than a fixed output level, the power supply becomes an amplifier. Carrying this one step further results in the PWM circuit employing four switches configured as an H-bridge providing bipolar output from a single supply. This does mandate that both load terminals are driven and zero drive results in 50% of supply voltage on both load terminals.

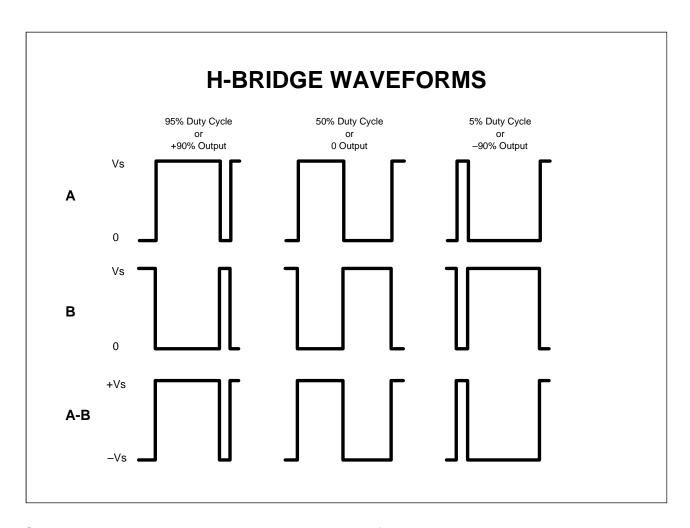

The H-bridge switches work in pairs to reverse polarity of the drive even though only one polarity supply is used. Q1 and Q4 conduct during one portion of each cycle and Q2 and Q3 are on during the remainder of the cycle.

Note that if Q1 and Q3 turned on simultaneously, there is nothing to limit current. Self-destruction would be only microseconds away. The fact that these transistors turn on faster than they turn off means a "dead time" needs to be programmed into the controller.

Changing duty cycle through 50% is a continuous function, meaning there is no inherent cause of crossover distortion as exists in a linear circuit. While the three waveforms seem a complex way to describe an analog drive signal, notice that waveform A is just the output of the "most basic" circuit we looked at earlier. Furthermore, A-B looks the same, the only difference is the bottom of the waveform is labeled "-Vs" rather than "0".

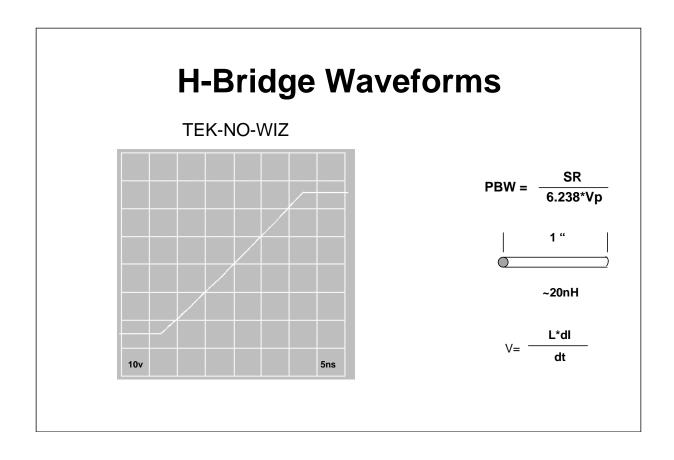

National had their FAST and DAMN FAST buffers, but they can't hold a candle to these guys. In fact, that's the problem with switchers--they move voltages and currents around so fast it's difficult to keep the noise down. Here are a few items you may not have had a chance to use lately.

From the analog world we borrow the equation relating slew rate to power bandwidth. If your PWM amplifier switches 50V in 25ns, the slew rate is 2000V/us. With peak voltage of 50V, this is over 6MHz. With 5 or 10 amps flowing, those transitions contain RF energy similar to a moderate radio transmitter. Spending a few minutes thinking like an RF designer may be worthwhile.

Currents are also changing very rapidly in these circuits. The picture above is of voltage, but keep in mind this voltage is on one end of an inductor where a power MOSFET just interrupted current flow. Look at the positive going transition: the lower MOSFET was conducting and the inductor is driving the voltage positive, above the positive supply, to maintain the previous current flow. The path will be through the body diode of the upper MOSFET, into the supply bypass capacitor. If current changes 5A in the same 25ns, two 1 inch capacitor leads will develop an 8V spike. On high speed PWMs this spike will cause the controller to freak out, rendering the circuit useless.

### Layout Sensitive? You Bet Your ...

Apex has an Eval Kit for every PWM model

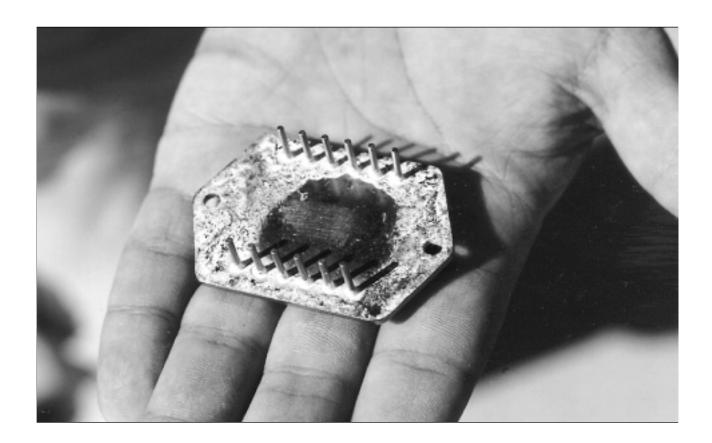

Evaluation Kits for PWM amplifier prototyping are a <u>must</u>. A bad layout will produce ample frustration and can cause dead amplifiers!

At a minimum, each kit provides a PC board, a way to get the amplifier plugged in, a moderate sized heatsink, and enough hardware to get it all put together. Several models also provide chip capacitors for low inductance bypass of the supplies.

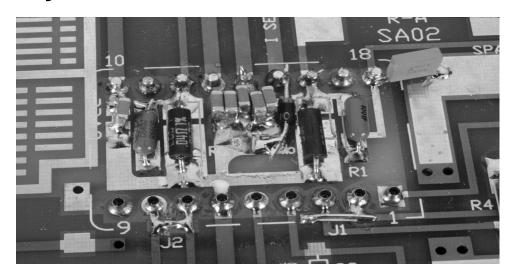

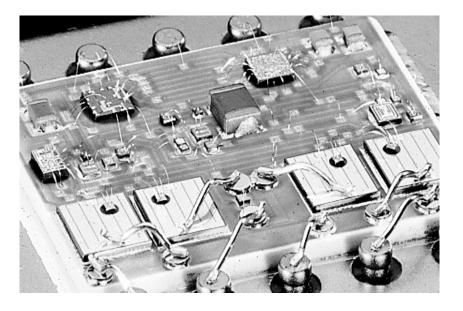

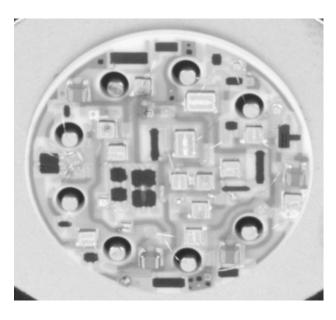

## **SA01**

The four huge transistors are the FETs of the H-bridge.

Not quite as obvious, is a unique advantage of hybrid construction which discrete designs can only dream of. Mounted right on top of each FET is a temperature sensor, exactly where the heat is generated.

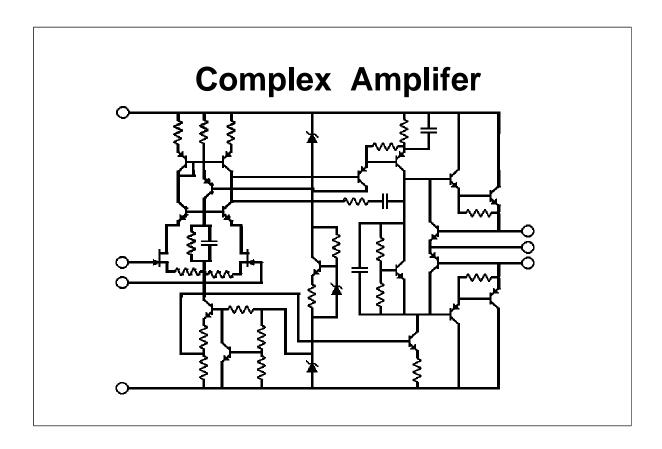

#### **SA01 BLOCK DIAGRAM** 7.5V REF OUT +Vs SUPPLY/ REFERENCE PWM THERMAL SHDN/FILTER **CURRENT LIMITS** SHUTDOWN **BOUT** DRIVERS A OUT **EA OUT** ERROR Isense **GND** As EA goes more positive, high state of A OUT increases and high state of B OUT decreases.

PWM circuits are taking the same general course of development traveled by op amps and many other electronic functions. Concepts were brought to life using discrete components and were followed by modules, hybrids and then monolithics. The first hybrid on the scene in PWM technology is the SA01 from Apex. The amplifier contains all the functions needed to implement a wide variety of control circuits.

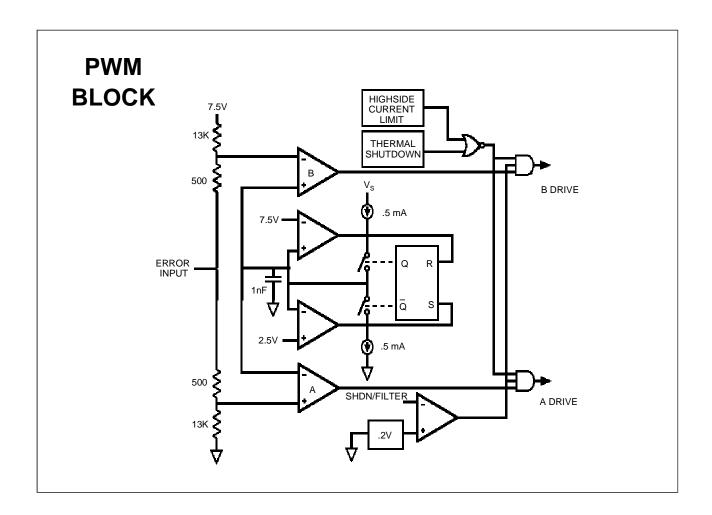

The oscillator portion of the PWM controller consists of two comparators, two switched current sources charging the timing capacitor and a flip-flop. When voltage on the timing capacitor reaches 7.5V, the upper comparator resets the flip-flop which opens the upper current source and connects the lower one. When the timing capacitor voltage reaches 2.5V, the lower comparator sets the flip-flop to start the next cycle.

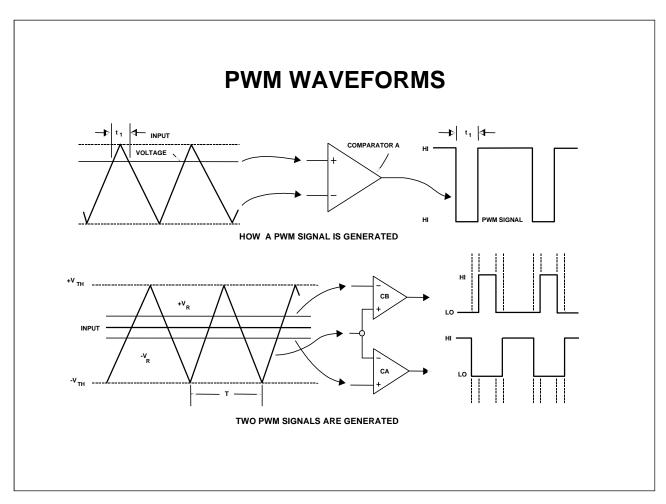

Comparators A and B modulate the driver output duty cycle based on the voltage relationship of the PWM input voltage and the very linear triangle. For initial examination of operation, imagine the  $500\Omega$  resistors are shorted. When the input voltage is midrange, there are equal portions of the triangle wave above and below the input, thus a 50% duty cycle is generated at each comparator output. When the input voltage moves half way between midrange and the 7.5V peak of the triangle, 1/4 of the waveform is above the input and 3/4 is below the input generating a 75% duty cycle at the A comparator. With the inputs of the B comparator looking at the input and triangle voltages in the opposite polarity, it generates a 25% duty cycle. Note the circuit is arranged such that a positive going input voltage results in a larger percent on time for the A driver.

With the  $500\Omega$  resistors actually in the circuit, the input voltage seen directly at the comparators is modified slightly, which modifies the duty cycle in a similar way. The A comparator sees a voltage a little more negative than the actual input. The basic function of positive going input creating a longer A duty cycle means this negative offset produces a slightly shorter duty cycle. In the same manner, the B duty cycle is also shortened to produce a dead band where all switches are off. Voltage drops across the two  $500\Omega$  resistors change as the input signal varies, but as one drop decreases, the other increases so total dead band time is relatively constant.

The and gates generating both A and B outputs can be disabled by either of two lines. The first of these lines represents activation of the thermal shutdown or the high side current limit. The second line is the comparison of the SHDN/FILTER input and a 0.2V reference. This configuration makes operation of both functions asynchronous and also allows operation to resume anywhere in the cycle when those lines return to their normal state.

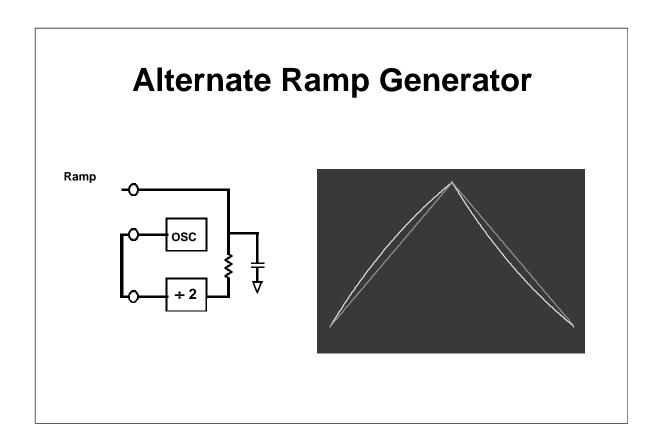

The switched current source method of ramp generation is elegant in that the slopes are very linear and the end points are set with reference quality voltages. The circuit above is much less expensive and has less non-linearity than one would expect at first glance.

When used to generate duty cycle information, the total time above and below the input signal level is what counts- -not the non-linearity of one individual slope. Another way to look at is that the upward slope has a non-linearity, the downward slope has another and the sum of both determine total non-linearity. It turns out there is a good amount of cancellation between the two such that the non-linearity of the sum is less than 1%.

We will discover other open loop errors are far greater; therefore, PWM amplifiers are almost never run open loop. Once the loop is closed, all of these errors are reduced to insignificant levels.

The alternate ramp generator also allows digital drive circuits to override the ramp waveform if desired.

### **Basic PWM Transfer Function**

Vo = output voltage

Vmid = ramp midpoint

Vin = input voltage

Vpk = 1/2 ramp Vp-p

Vs = supply voltage

lo = output current

Ron = total on resistance

- Poor load regulation

- No line regulation

- Temperature sensitive

- Close the loop!

The PWM controller output is duty cycle information only, It is proportional to the input signal level with respect to the end points of the ramp. The power MOSFETs convert this to power pulses and the filter integrates the area under the pulses to provide an analog output. Given a fixed duty cycle, the amplitude of the pulses, and hence the analog output level, is controlled by the power supply voltage and the MOSFET losses.

Those of us acustomed to working with power op amps take power supply rejection for granted; at least at low frequencies, so supply voltage changing a few percent is of no concern. In a similar fashion, we tend to not worry about op amp output impedance because it is reduced by the loop gain of the amplifier. Notice the assumption that nobody runs an op amp open loop; at least when looking for an analog output.

OK, we have learned that open loop performance of a PWM is very different than an op amp: its open loop gain is not ≅100db, it is the ratio between the peak ramp voltage and the supply voltage and its supply rejection is not 60 to 100db, it is zero db. Accuracy and open loop operation of a PWM amplifier do NOT go together.

Closing this loop can be done locally in the voltage mode and with most models in the current mode. The alternative is closing the loop with system components. This often involves mechanical components, velocity or position sensors and a computer.

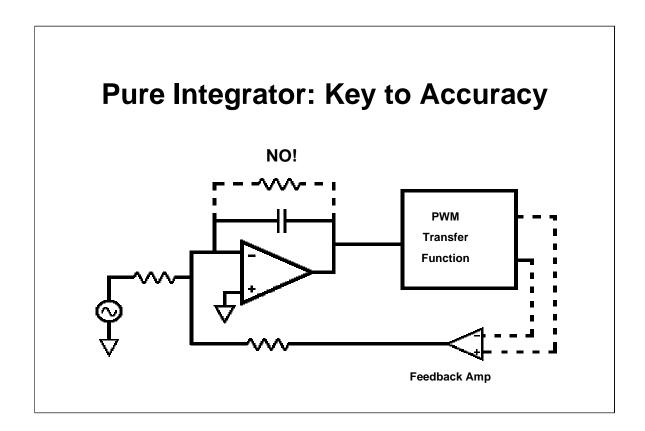

Lets go back to some basic op amp theory for a moment: The open loop gain (the voltage ratio of the output pin to difference of the input pins) of an op amp is extremely high (100db is 100K:1). This means the input pin voltage above is approaching zero. If there is no DC feedback and no current in or out of the input pin, then current through the two resistors must be equal. The PWM output is accurately scaled to the input signal.

The beauty of this analysis is the lack of discussion about the output level of the integrator. As long as all the circuit scaling insures we do not saturate any stage, the integrator takes care of all the variables: supply changes, ramp non-linearity, MOSFET losses, and changes in load impedance.

Sometimes it is a temptation to add resistive feedback. If this is done, DC feedback current lowers accuracy. To find this current we must know the output voltage of the integrator. Start with the PWM output and go backward through the transfer function. The worst case is when the output is near the supply voltage which demands the integrator output be near one of the ramp peaks. The resulting DC feedback current is now causing a mismatch between the input signal and the feedback amplifier currents. Not only is there a gain error, but supply variations and ramp inaccuracies creep in.

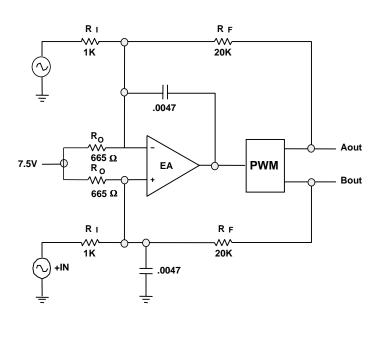

# PWM VOLTAGE CONTROL

This is a differential input, voltage controlled output circuit resembling the familiar differential op amp configuration. Signal gain is simply RF/RI. Two pull-up resistors are used to bias error amplifier inputs within the common mode range. Select this value to get 5V bias when both inputs are zero, and both outputs are 1/2 the supply voltage (50/50 duty cycle.) At zero drive to the load, this differential stage is rejecting 1/2 the supply voltage present on both outputs. This means resistor ratio matching becomes critical. It should also be noted that even though the signal gain is 20, the gain of offset errors is 50 because the effective input resistance is the parallel combination of the signal input resistor and the pullup resistor.

While the specific load is not indicated here, it must be remembered that the SA01 output needs to be filtered. In fact, if the load were purely resistive, this circuit will NOT work! The load would receive full power one direction the first half cycle and full power of the opposite polarity the next. Many common loads such as motors and magnetic bearings will provide adequate filtering on their own. If this is not the case, filtering must be added.

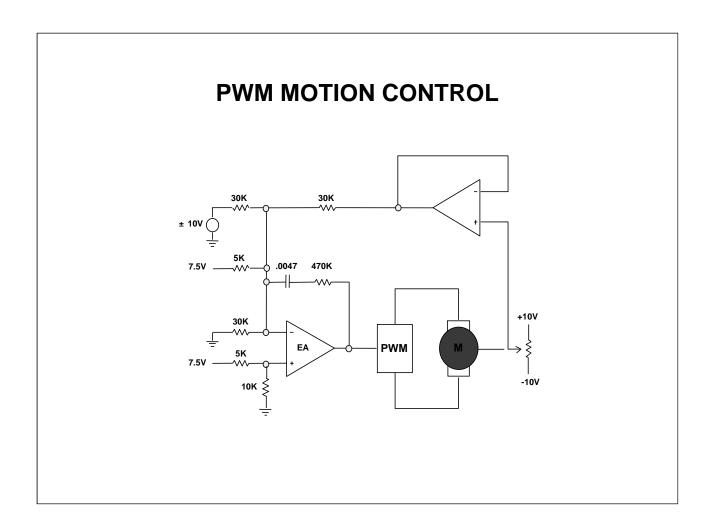

While one of the simplest forms of position sensing is shown here, options such as optical encoders, LVDT sensors, tachometers and variable capacitance transducers are all viable ways to sense speed or position. Again, error amplifier inputs are biased to 5V. While 20Kohm input and feedback resistors would have set proper gain and static biasing for the inverting input, they would have allowed common mode violations. This could happen if the system was at one position extreme while a very quick command came in to travel to the opposite extreme. The three 30Kohm resistors prevent common mode problems by increasing impedance from the summing junction to the two 10V signal levels (at the output and at the input) while adding an impedance to ground to form an equivalent 10Kohm impedance to match the 10Kohm leg on the non-inverting input.

The 0.0047µF and 470Kohm values shown here are ballpark values only. In closing the loop in this manner, the inertia of the motor, gear train and load, plus the responses of other electronic components of the application, all enter into the stability/response considerations.

# **Compare: PWM & Linear Amps**

V or I input OK OK OK OKV or I output Single/Dual Single **Supplies** Max Power Several KW Fractional KW Efficiency High Low Noise High Low Speed High Low

Think about the two previous pages a moment.

They are both basically op amp circuits where the driving op amp has a specialized output stage labeled PWM. In fact there are many applications where linear and PWM solutions would both work. The keys to the decision may be on the last two lines above: IF THE APPLICATION DOES NOT REQUIRE LOW NOISE AND HIGH SPEED, PWM AMPLIFIERS CAN PROVIDE A SOLUTION.

The next item to consider is cost. On a cost per watt capability basis, PWM amplifiers are generally less expensive than linears. With PWM capability starting at 200W, they are not the most likely candidates for a 5W job. At a few hundred watts, PWM amplifiers are very attractive. In between these levels, you may want to think more about the options because both linear and PWM amplifiers will likely work.

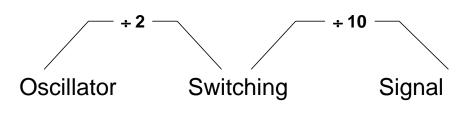

The alternate ramp generator illustrated the relationship between oscillator and switching frequencies. Some PWM data sheets (such as the SA01) do not mention oscillator frequency because there is no divide by two circuit.

Signal frequency is that of the power drive to the load, power bandwidth. Between the load and the PWM amplifier is the low pass filter (or at least the model of one if the load is also the filter). On the input side of the filter we have the switching frequency. We then go down the slope to a point where the attenuation is adequate. The frequency band we cover while going down the slope is required spacing between the switching and signal frequencies.

Pure theory says filter slope can be increased simply by adding more poles. This is true to a point. We would probably question an eight pole filter in the small signal world. Do you really need that? Can you find high enough quality components to make it work? Can you afford it in terms of size and cost?

In the PWM world these questions are not only valid but are many orders of magnitude more important because power levels have gone from mW to KW! Rule of thumb: Allow a decade between switching and signal frequencies.

| Filter   | Desia      | n for l | WM A | mplifi      | ers     | READ      | ME          | Us  | ina f | he Co   | mplex    | Load:  |

|----------|------------|---------|------|-------------|---------|-----------|-------------|-----|-------|---------|----------|--------|

|          | TION!      |         |      | Application |         |           |             |     |       |         | piex     |        |

| Input D  | ata        |         |      |             |         |           |             |     |       |         |          |        |

|          | SA03       |         |      | Order       | Calcula | tion      |             |     | 60 L  | oad All | Data For | N=1    |

| Vs       |            | Volts   |      | Atten. @    |         | 39.085    | db          |     | 61.L  | nad All | Data For | N=2    |

| Fsw      | 22.5       | KHz     | 22.5 | N(exact)    |         | 2.6052    |             |     |       |         |          |        |

| Fmin ไ   | 0.001      | KHz     |      |             |         |           |             |     | 62 L  | oad All | Data For | · N=3  |

| Fcutoff  | 4          | KHz     |      | N(recom     | mended) | 3         |             |     | 63 L  | oad All | Data For | N=4    |

| Rload    | 10         | Ohms    |      |             |         |           |             |     | 641   | and All | Data For | · NI=5 |

| Cload    | _          | uF      |      | Matchi      | ng netv |           |             |     |       |         |          |        |

| Lload    | -          | mH      |      | Cm =        |         | uF        |             |     | 83 L  | oad All | Data For | N=6    |

| Vripple  |            | Vpk     |      | Lm =        | _       | mH        | Read        |     |       |         |          |        |

| Signal   |            | Units   |      | Rm =        | 10      | Ohms      |             | No  |       | Auto S  | weep or  | Load?  |

| Sig as ? | v peak     | Note/W  |      |             |         |           |             |     |       |         |          |        |

| Notes:   |            |         |      |             |         |           |             |     |       |         |          |        |

| votes.   |            |         |      |             |         |           |             |     |       |         |          |        |

|          | 46 Print I | Filter  |      |             | 55 Sho  | w Attenua | ation in db | 8.% |       |         |          |        |

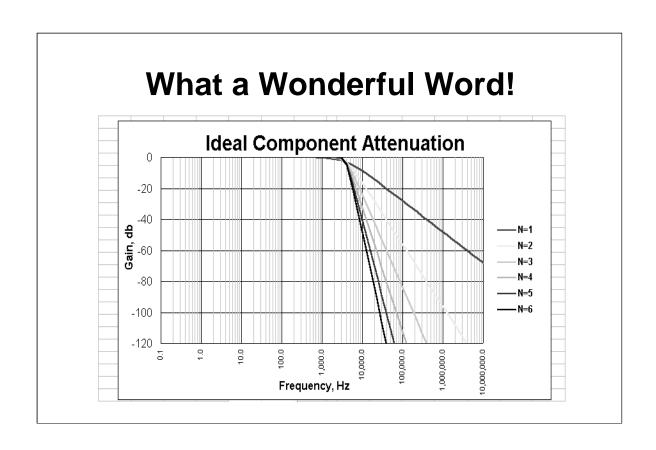

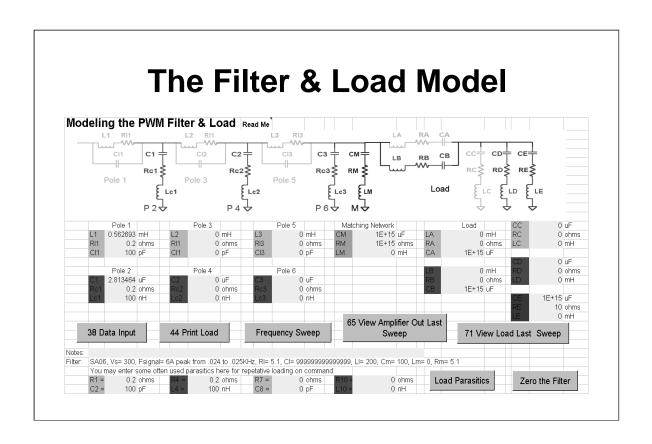

So maybe filter design is not at the top of your list of most cherished jobs. Application Note 32 and the Power Design spreadsheet can help. Enter data describing the amplifier circuit, the load and desired attenuation. Placing the cursor in cells with red triangles will display notes of explanation. The order Calculation section converts your maximum ripple spec into db attenuation and by examining the switching and signal frequencies, it calculates the order, or number of poles needed. The matching networks calculated will cause reactive loads to appear resistive to the output of the filter, Finally, the actual filter components are calculated and the response is graphed.

|       | Sir                         | ngl                         | е         | E    | ndo          | ed        | 1 | VS      | D          | iff€         | ere    | ent       | ia        |           |

|-------|-----------------------------|-----------------------------|-----------|------|--------------|-----------|---|---------|------------|--------------|--------|-----------|-----------|-----------|

|       |                             | Calcula                     |           |      |              |           |   |         |            |              |        |           |           |           |

|       |                             | tial Filter                 |           | Sing | le-ended Fil | ter       |   |         | Differen   | tial Filter  |        | Single-er | nded Filt | er        |

| N = 1 | L=                          |                             |           | Jing | 0.3979       |           |   | N = 2   | L=         | 0.2813       |        | -mgio oi  | 0.5627    |           |

|       | _                           |                             |           | Amp  | s out of the |           |   |         | C =        | 5.6269       |        |           | 2.8135    |           |

|       |                             | ut for thern                |           |      |              | 1.2566    |   |         | P-P Irip   | ple =        |        | Amps ou   |           |           |

|       |                             |                             |           |      |              |           |   |         |            | it for therr |        |           |           | 0.8886    |

| N = 3 | L1 =                        | 0.2984                      | mΗ        |      | 0.5968       | B mH      |   |         |            |              |        |           |           |           |

|       | C =                         | 10.61                       | uF        |      | 5.305        | i uF      |   | N = 4   | L1 =       | 0.3045       | mH     |           | 0.609     | mΗ        |

|       | L2 =                        | 0.0995                      | mΗ        |      | 0.1989       | mH        |   |         | C1 =       | 12.551       | uF     |           | 6.2755    | uF        |

|       | P-P Irip                    | ple =                       | 3.351     | Amp  | s out of the | amplifier |   |         | L2 =       | 0.2153       | mΗ     |           | 0.4307    | mΗ        |

|       | Avg. lout for thermal calcu |                             |           |      |              | 0.8378    |   |         | C2 =       | 3.0454       |        |           | 1.5227    |           |

|       | _                           |                             |           |      |              |           |   |         | P-P Irip   | ple =        | 3.2838 | Amps ou   | t of the  | amplifier |

| N = 5 | L1 =                        | 0.3074                      | mH        |      | 0.6148       | mH        |   |         |            | ıt for therr |        |           |           | 0.821     |

|       | C1 =                        | 13.484                      | uF        |      | 6.7418       | 3 uF      | _ | Read me | e if you p | olan to us   | e N=6  |           |           |           |

|       | L2 =                        | 0.2749                      | mH        |      | 0.5499       | mH        |   | N = 6   | L1 =       | 0.3089       | mΗ     |           | 0.6179    | mH        |

|       | C2 =                        | 7.1174                      | uF        |      | 3.5587       | uF        |   |         | C1 =       | 14           | uF     |           | 7         | uF        |

|       | L3 =                        | 0.0615                      | mΗ        |      | 0.1229       | mH        |   |         | L2 =       | 0.3089       | mΗ     |           | 0.6179    | mH        |

|       | P-P Irip                    | ple =                       | 3.2532    | Amp  | s out of the | amplifier |   |         | C2 =       | 9.562        | uF     |           | 4.781     | uF        |

|       | Avg. lo                     | Avg. lout for thermal calcu |           |      |              | 0.8133    |   |         | L3 =       | 0.1508       | mΗ     |           | 0.3016    | mH        |

|       |                             |                             |           |      |              |           |   |         | C3 =       | 2.0595       |        |           | 1.0297    |           |

|       | 56 Sho                      | w Attenua                   | tion Gran | oh   | 38 D         | ata Input |   |         | P-P Irip   | ple =        | 3.2369 | Amps ou   | t of the  | amplifier |

|       |                             | 30 Onow Attenuation Grap    |           |      |              |           |   |         |            | ut for therr |        |           |           | 0.8092    |

Single ended filters have at least an inductor between one output terminal of the PWM amplifier and the load while the other terminal of the load is tied directly to the other output of the PWM. Differential filters have at least an inductor between both PWM outputs and the load terminals.

While single ended filters have the advantage of using the same total inductance, but one fourth the total capacitance of the differential filter, this is not the end of the story. Unless the load is physically small (the electrical radiating surface) and physically close to the amplifier, the raw square waves will be broadcast to any circuit willing to listen. One PWM output goes directly to the load and with even ordered filters, both load terminals have AC tied to them. How long is your cable (transmission antenna) to the load?

The analysis function we will look at next handles only single ended filters. The data above shows how to translate to differential values if desired. Capacitors for differential will be twice those of single ended and inductors will be half.

"Ideal" is a great word. In this case it means most of the work still lies ahead in finding components which work as advertised in the MHz range and whose losses won't kill you at high current levels.

For capacitors, this usually means two and more often three parallel devices: high value/low frequency, low value/high frequency and lower value/higher frequency. You will probably want ceramic for the highest frequency ranges. For the larger capacitance values tantalum, or electrolytic types at higher temperatures, will work well.

Finding suitable inductors is also challenging. Air core inductors get away from the magnetic saturation problem and they have less tendency to become dummy loads at high frequency. The down side will be more turns of wire and more copper losses. When adding a magnetic core make sure the material can handle the high frequency components of the square wave at the switching frequency and can accommodate the flux density of the peak currents to be delivered to the load.

Pressing one of the "Load All Data" buttons on the PWM Filter sheet transfers your application to the PWM Power sheet. We already know how to translate component values to differential mode for hardware if desired, so the single ended only capability of the analysis will not be a problem.

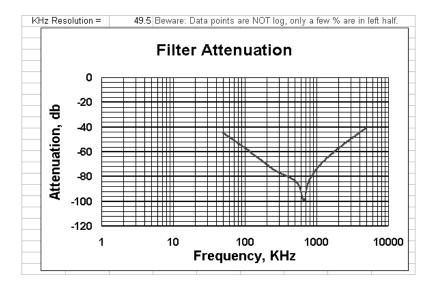

Attenuation is about as expected up to 200KHz, but then the parasitics come into play. We learned earlier that the extremely fast transition times of the PWM amplifiers means high frequency content is powerful well into the megahertz range. This graph is telling us spike content at the filter output is far from ideal. Is this OK? Or should we spend more on better filter components?

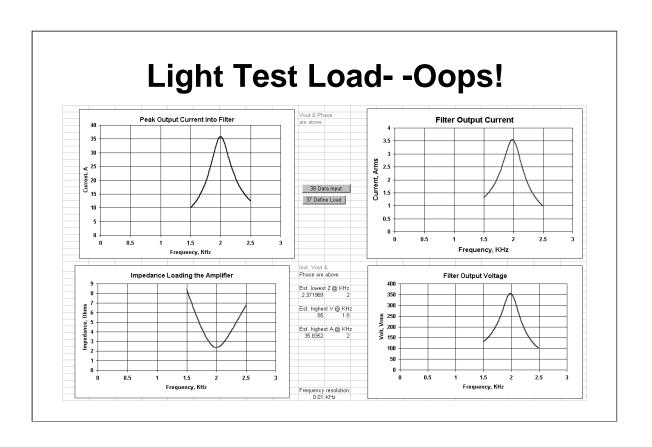

So, you're an old hand with linear power circuits; you fire up the prototype with a light load to make sure everything is working before connecting the real load.

While this procedure is commendable for linear drives and *may* work fine of a PWM drive, watch out for tuned circuits in the filter/match network/load. Replacing the designed 10 ohm load with 100 ohms produces the graphs above. At 2KHz impedance drops to ~2.5 ohms, peak current tops 35A, load voltage is ~355V and load current is 3.5A. 1200W delivered to the *light* 100 ohm load!

#### Be careful- -deadly voltages easily generated.

The second order filter driven at the designed cutoff frequency, with no load, is a series resonant circuit which presents a theoretical zero impedance to the amplifier and develops a theoretical infinite voltage at its center.

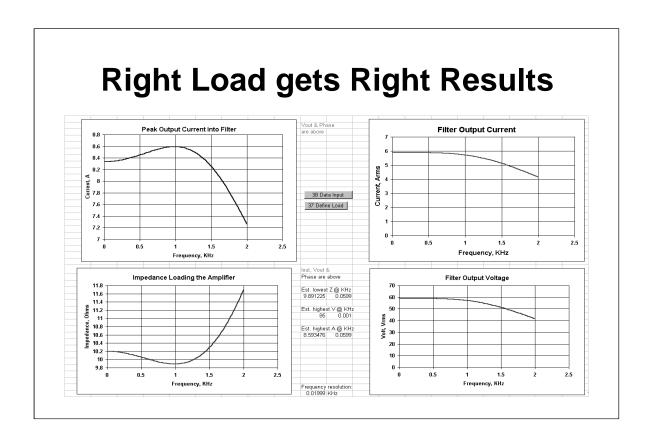

With proper termination of the filter we get a little min-band peaking amplifier output current but the catastrophic potential of bad filter termination has gone away.

While this operation is *proper*, is it what you wanted? The cutoff frequency of the filter is where the load voltage is down 3db. does -3db equal .707 or .5? Both, .707 is the voltage or current ratio and .5 is the power ratio. Many times the half power at maximum frequency is not acceptable.

Some designers routinely start their filter calculations at twice the required frequency of the application.

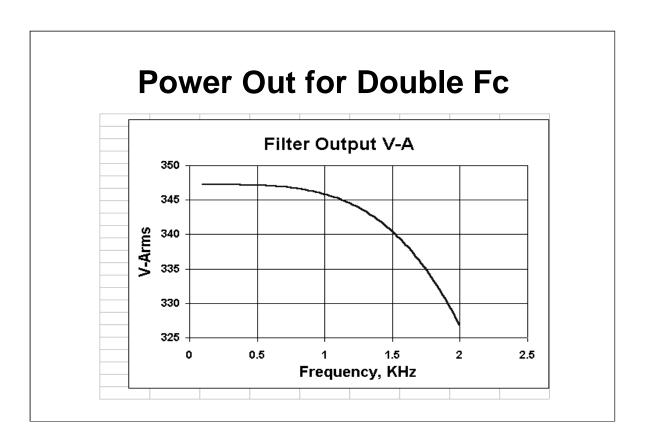

Doubling the design cutoff frequency of the filter enables the circuit to deliver a lot more power at the desired 2KHz.

Yes, you could double again to achieve an even flatter pass band. No, there is no free lunch. Every time you move cutoff frequency up, you allow more switching frequency power in the load. Yes, you can add more poles to the filter. The question becomes one of cost in terms of money, extra loss in the filter, size and weight.

While the conjugate matching network performs almost like magic in terms of forcing the attenuation graph to near text book shape, there is a cost involved. This cost is slight when the load is mostly resistive but power dissipated in this network approaches power delivered to the load as the load approaches pure reactance.

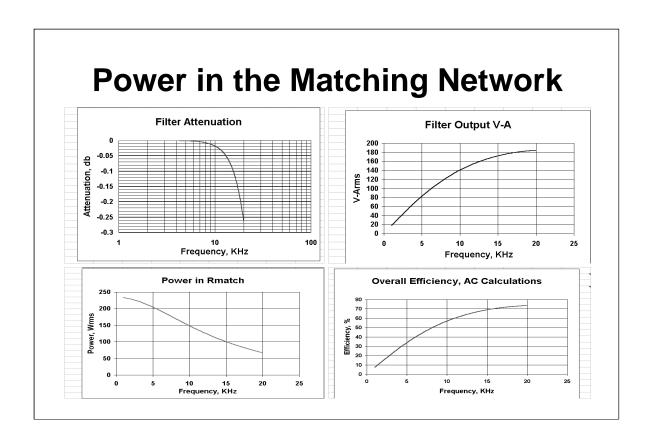

These graphs are for an application driving a 1uF piezo stack with 12 ohms series resistance, to 75V peak from 1KHz to 20KHz. The filter cutoff frequency was designed for 40KHz providing quite flat response. The V-A output falls at low frequency because the load impedance is increasing. To keep filter termination impedance flat, the matching network impedance moves in the opposite direction giving rise to large power levels in the matching network resistor. As this power is not delivered to the load, efficiency is far from the desired level.

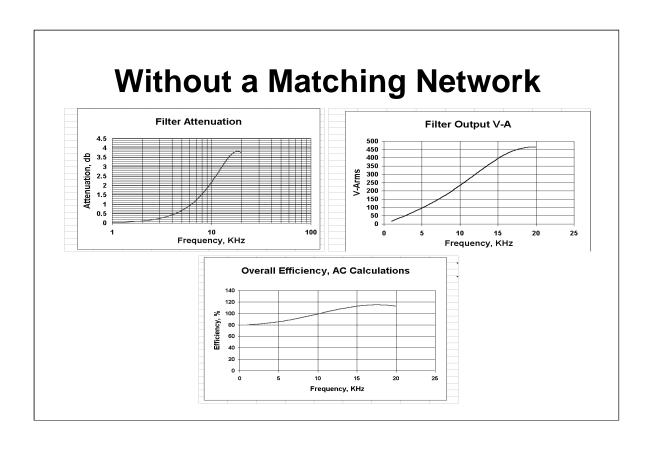

With no matching network we cannot lose any power there, but this leaves the filter with an improper termination. The result is a resonant circuit causing almost 4db peaking. In terms of V-A in the load near the upper end of the band, power goes from ~180 to over 450V-A. The efficiency graph looks like a patent should be applied for. The reason for this is recirculating currents in our newly formed resonant circuit.

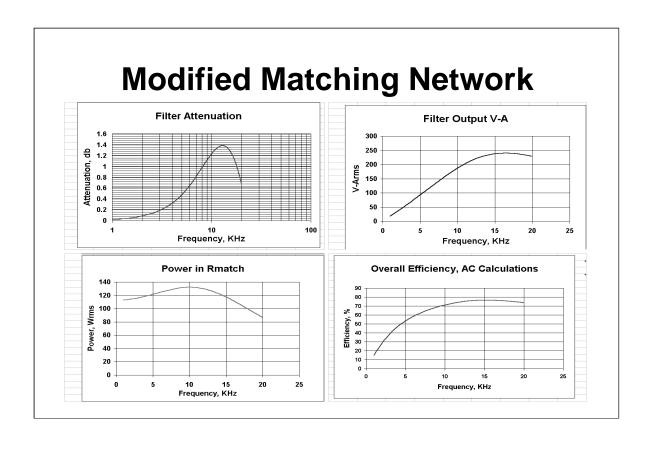

Here lies part of the beauty of the Power Design spreadsheet; it took more time to prepare this slide than it did to discover that doubling the resistor value in the matching network may provide a workable compromise.

Peaking at the load is down substantially from not using any network and wasted power is down substantially from using the ideal network.

# Only Need ½ a PWM Amp?

- Unipolar, usually grounded loads

- PPS, TEC, 3Ø motor

- Heater, uni-directional speed control

- · Active loads, CD weld charger

- Saves ~½ internal losses

- Saves ~25% on cost

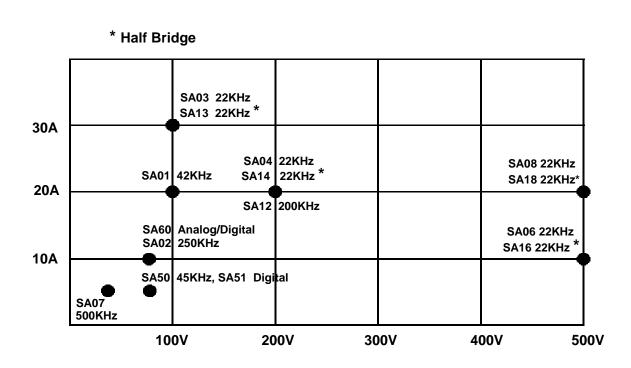

- SA13, 14, 16

While all Apex PWM amplifiers can be configured in the half-bridge mode, three models are built that way to save you money. These models are ideal for applications requiring only unipolar drive. This means the load is usually grounded. Three amplifiers driving a three phase motor, and active load circuits are exceptions to this rule.

Since load current flows through only one MOSFET at a time rather than two, efficiency is increased. By leaving out some of the internal components, a cost savings is realized.

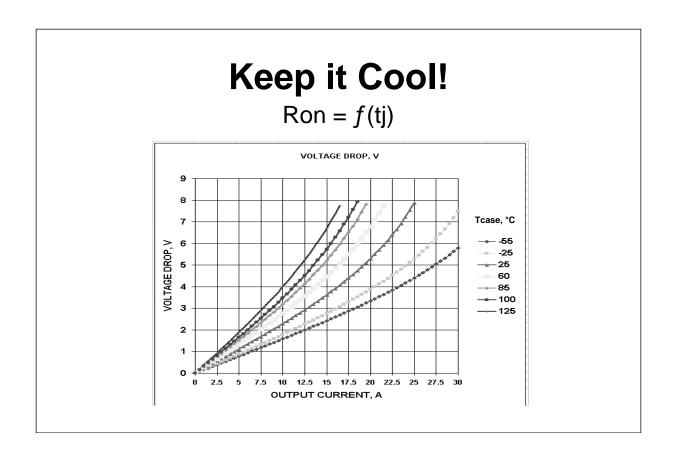

The "on" resistance of a power MOSFET increases a little over two times as junction temperature rises from +25°C to +150°C. This means a larger heatsink increases both output capability and efficiency. If there's good news to this story it's the non-linearity of the curve: The first few degrees we lower temperatures buys the most. Here's a way to approach the problem.

First order power dissipation in the PWM is a function of the output current and the voltage drop at that current. This is the PWM advantage over linear power delivery; supply voltage is not part of the equation. Start with the 60°C curve (interpolate if required). Find your current (PEAK if below 60Hz, otherwise RMS) and read the voltage drop. The product is power dissipation. The voltage drop divided by supply voltage approximates efficiency (quiescent current of both Vcc and Vs will reduce this a little). The heatsink rating is 60°C minus ambient temperature, divided by power.

Are these numbers all affordable? Remember that a bigger heatsink actually reduces the watts to be dissipated (unlike linear systems).

|                       | PWM              | l Po                                 | owe            | r D                      | iss          | ipat          | tior       | 1        |         |

|-----------------------|------------------|--------------------------------------|----------------|--------------------------|--------------|---------------|------------|----------|---------|

|                       |                  |                                      |                |                          |              |               |            | _        |         |

| Calculating P         | ower Dissi       | pation                               | for Apex       |                          |              |               |            |          |         |

| Model SA03            | Read Me          |                                      | Ta max = `     | 25                       | Tj max =     | 150           | Tc max =   | 85       |         |

| Power for Sine Wav    | e Outputs        |                                      |                |                          |              |               |            |          |         |

| √s <b>"</b> 90        | ) Volts          |                                      | Fswitch =      | 22.5                     | KHz          |               | Iripple =  | 0.444292 | Α       |

| Fmin 0.001            | KHz              |                                      | lq Vcc =       | 0.08                     | А            |               | lout =     | 8.335271 | Α       |

| Fmax 2                | 2 KHz            |                                      | Piq Vcc = "    | 1.2                      | W            |               | lfet =     | 8.347104 | Α       |

| Sig S                 | 5 Units          |                                      | lq ∨s =        | 0.0665                   | Α            |               | Fhotspot = | 0.0599   | KHz     |

| Sig as ? V peak       | Note∕W           | 1                                    | Piq Vs =       | 5.985                    | W            | Minimum H     | eatsink:   | 2.608519 | °C/W    |

|                       |                  | Max d                                | elta Tj =      | 125                      |              | Max delt      | a Tc =     | 60       |         |

| General Procedure:    | First Filter Des | First Filter Design Tune the         |                | er Select the heatsink   |              |               |            |          |         |

| Actual HS:            | 1                | °C/W                                 |                | _                        |              |               | R PchFET   | 0        | Ohms    |

| Approx. Power Out     | 354.1725495      | Wrms                                 |                | •                        |              |               | R NchFET   | 0.128717 | Ohms    |

| Estimated Internal Pw | r 19.63693269    | W                                    |                | •                        |              |               | Rwire      | 0.05     | Ohms    |

| Estimated Case temp   | 45.27818631      | °C                                   | Read me        | 00 V/io                  | v Overall Et | ficionou I    | Rtotal     | 0.178717 | Ohms    |

| Est. Junction temp    | 49               | °C Read                              | me             | - oz viet                | v Overali 🗀  | liciency      | D.C.max    | 99       | %       |

| Efficiency @ Fhotspot | 94.74680723      | % (AC An                             | nplifier Only) | NA                       | % (DC Am     | plifier Only) | Vpk out    | 85       |         |

| Est. Vpk capability   | 87.56261428      | ν `                                  |                |                          | `            | ,             | lpk out    | 8.593476 |         |

|                       | .00 [-:          | Marali Co                            | 004 4- 214     | I_ DI_ 10                | OI— 000000   | 000000000     | LI= 0. O   | 00000000 | 000000  |

|                       | 90, Fsignal= 85  | v peak troi                          | m .uu i to 2Ki |                          |              | 1999999999    | LI= U, CM= |          |         |

| 37Define Load         | Sweep the        | 65 Viev                              | w Amn Out      | 68 Print Data 71 View Lo |              |               | he         |          | je down |

|                       | Frequency        | Frequency 65 View Amp Out Last Sweep |                |                          |              | Last Swee     |            | TOT      | charts. |

|                       |                  | Lasi                                 | . олгеер       |                          |              | _ast 04466    | , P        |          |         |

Did someone complain about lack of detail on the previous page? Here they are, and the inputs were transferred from the PWM Filter sheet. If you change a green cell value, blue cell answers will not be valid until you run a frequency sweep.

If you get errors when you do this at home, check the READ MEs. You need the Analysis Toolpak add-in. Now you can see in the upper half, quiescent powers calculated, plus output current, FET current, hotspot frequency and best of all, minimum heatsink.

A little lower, notice I have already input an acceptable heatsink value and operating points have been calculated. Please read the comments. The Power Output is assumes a properly terminated zero loss filter and a power factor of 1 in the load. Use button 82 to see efficiency including filter losses. If you enter too small a heatsink, most of these answers will be forced to ridiculously large numbers and a red TOO HOT warning will appear.

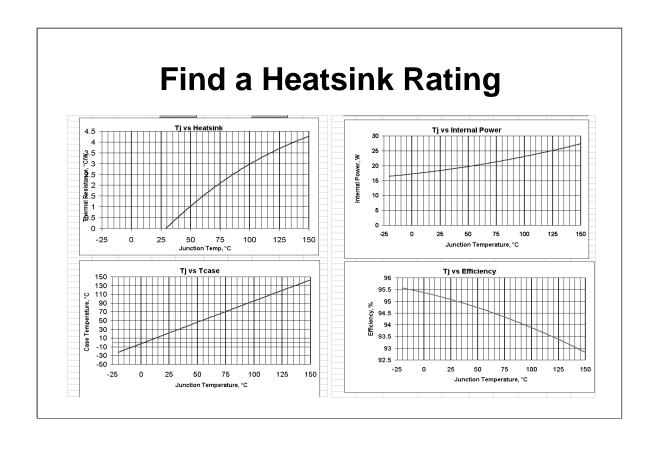

In the upper left graph it looks like a quite small heatsink will keep junction temperatures below maximum. However the graph below says there is little difference between junction and case temperatures and we surely want to keep case temperature a lot lower than 150°C.

On the top right we see that internal power dissipation of the amplifier changes with junction temperature - - or with the size of the heatsink. Below we see this same effect expressed in terms of efficiency. This is a relatively low power PWM application. With higher power applications the percentage point change shown on this graph will increase.

### Find a Heatsink

|                 | ing an Apex Heats       | INK See ACC    |                   | KIVIATION data s  | neet for spe  | cifications | 3    |

|-----------------|-------------------------|----------------|-------------------|-------------------|---------------|-------------|------|

| Thermal F       | Resistance              |                | Package           |                   |               |             |      |

| 2.3             |                         |                | MO127             | Update F          | Result        |             |      |

| READ MI         |                         |                |                   |                   |               |             |      |

| MO127 Heat-Sink |                         |                |                   |                   | Velocity Calc | ulator:     |      |

|                 |                         |                |                   |                   | 100           | CFM         |      |

| Apex PN         | Price /1pc USD Domestic | No Wind Rating | Wind Speed in FPM | Water Flow in GPM |               |             |      |

| HS06            | \$42.30                 | 0.96           | 0                 |                   | 10            | Inch Diam   | eter |

| HS11            | \$214.80                | 0.675          | 0                 | 0                 | 183.3464944   | FPM         |      |

| HS18            | \$81.00                 | 1              | 0                 |                   |               |             |      |

|                 |                         |                |                   |                   | 9.5           | Inch Width  | 1    |

|                 |                         |                |                   |                   | 12            | Inch Lengt  | th   |

|                 |                         |                |                   |                   | 126.3157895   | FPM         |      |

Believe me, heatsinking is NOT the most easiest science in our universe.

Let's start with "the" heatsink rating. The HS03 is rated at 1.7°C/W in free air. True, when power dissipation is about 45W, but check the actual curve at 10W and you'll find a rating more like 2.3°C/W. On top of that, "free air" means no obstructions to air flow and the flat mounting surface must be in the vertical plane. Demands for higher performance in smaller packages can be at odds with optimum heatsinking. Poor installation choices can easily reduce effectiveness 50%.

Moving on to this selector software. Air velocity curves from the heatsink data sheet (when available) have been approximated with polynomial expressions. While these errors are minor compared to the previous paragraph, it would be good to allow 10% for velocity ratings over 150 feet per minute and 20% below that.

Adding a fan to your design enables you to use smaller heatsinks. Please remember: Most fans are rated in cubic delivery and this rating varies with working pressure. A 5 inch diameter fan delivering 100 CFM produces over 700 FPM right at the fan. If this air is flowing through a 19 x 24 inch rack, theoretical velocity is down to 32 FPM, will vary with location and goes lower as the rack is sealed tighter.

The bottom line: Without case temperature measurements, your design effort is NOT complete!

Data as of January 2000.

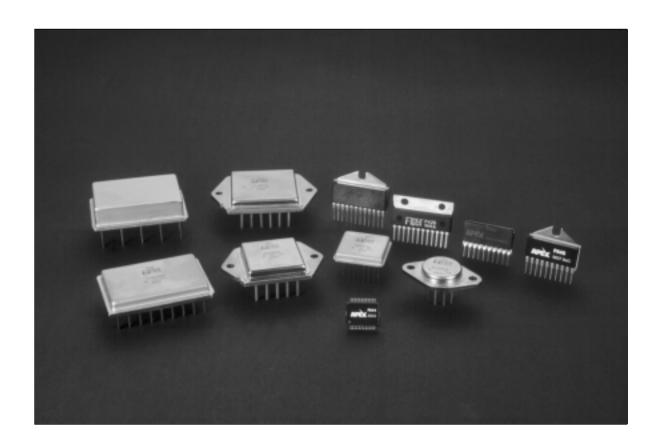

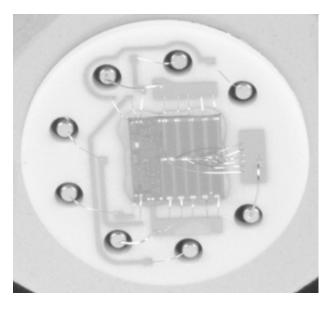

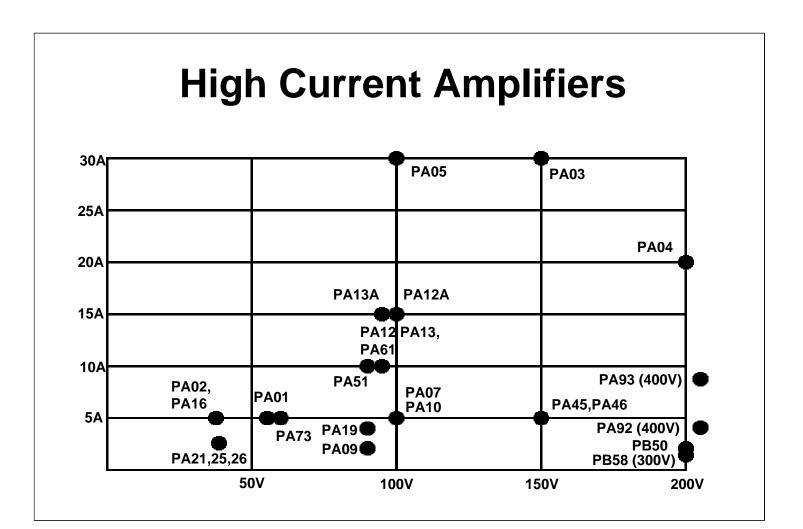

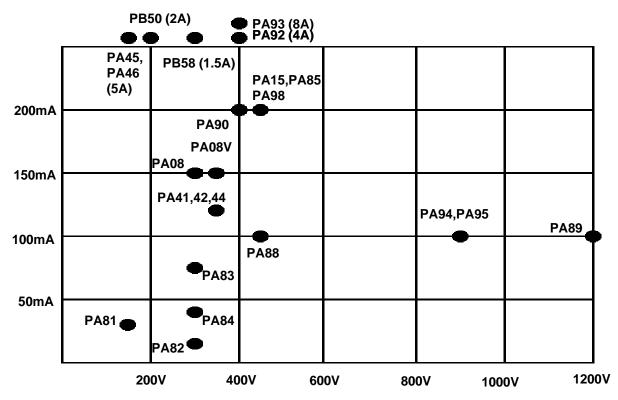

APEX is the industry leader in monolithic and hybrid high current and high voltage power amplifiers. With more than 70 different models, we provide solutions for designs requiring output current greater than 1A or total supply voltages above 100V. When considering the cost versus performance trade-offs between using a power op amp versus discrete circuits, you must figure in design time, troubleshooting, procurement as well as production costs, not to mention labor, as well as the reliability factors. More often than not, you will find *it does not pay to be discrete!*

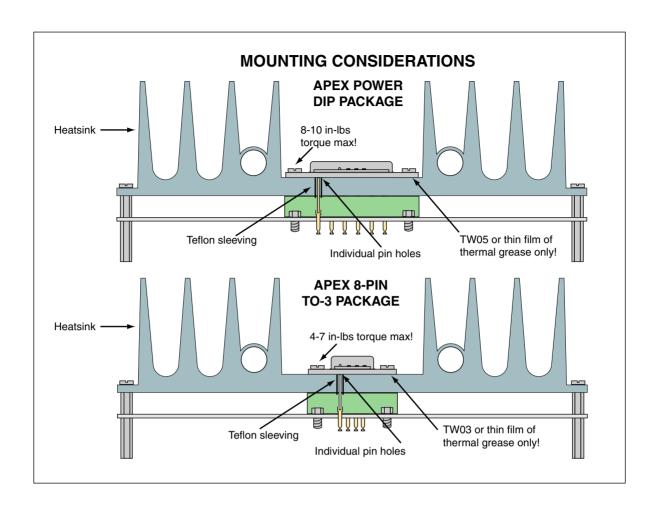

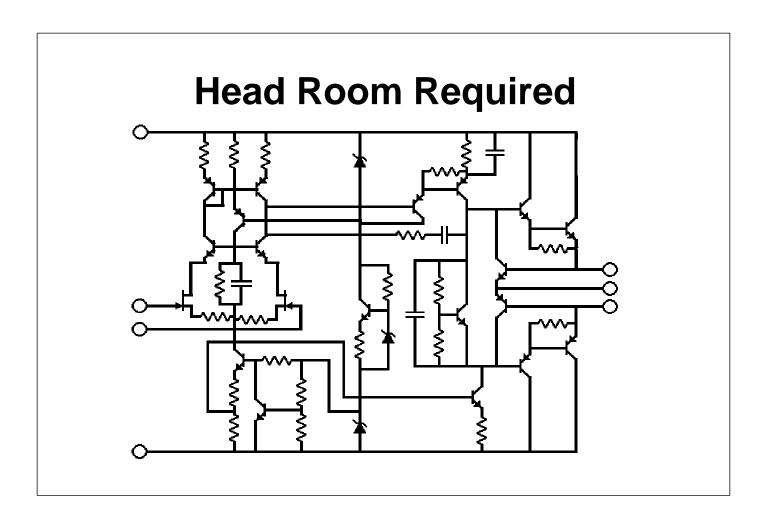

Apex offers a wide variety of packaging solutions to meet your needs. The 8-pin TO-3 is cost effective and easy to heatsink. The 10 and 12 pin Power Dips share the same rugged construction features but offer larger area for increased power handling capability. The power SIPS are easy on real estate and their flat back mates to a wide variety of heatsink options. The surface mount packages promise the ultimate in circuit density. All models featuring monolithic construction are also offered in chip form.

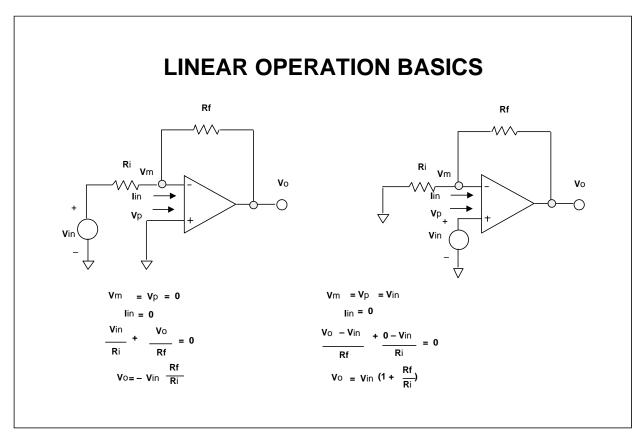

Before we discuss non-linear operation, we will cover some of the basics of linear operation for that mythical creature, the "ideal op amp". The three most important characteristics of an ideal op amp are:

- 1. Infinite input impedance

- 2. Zero output impedance

- 3. Infinite open loop gain

Let's review the inverting configuration in light of these three basic characteristics. #1 dictates that the input current into the op amp is 0. #3 implies that any voltage appearing between the input terminals will result in infinite output voltage. The resistive divider action of Rf and Ri causes a portion of the output voltage to be fed back to the inverting input. It is this NEGATIVE FEEDBACK action coupled with #3, open loop gain, that keeps the voltage between the two inputs at zero.

In the inverting configuration, this results in a "virtual ground" node. The concept of a virtual ground, coupled with the zero input current flow, allows the "closed loop gain" or transfer function of the circuit to be easily calculated. Current flow in Ri is equal to Vin/Ri. The same current is forced to flow through Rf, giving an output voltage of -linRf.

In the non-inverting amplifier, the infinite open loop gain of the amplifier, coupled with negative feedback, force the inverting terminal to be equal to the non-inverting terminal. This sets up a voltage across Ri which develops a current that also flows through Rf. Therefore, the total output voltage is s Vin/Rin current times the series combination of Rf and Ri.

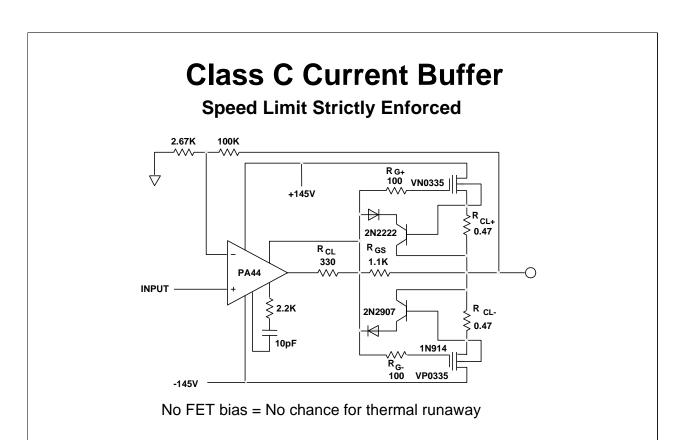

# **Class C Output Stages**

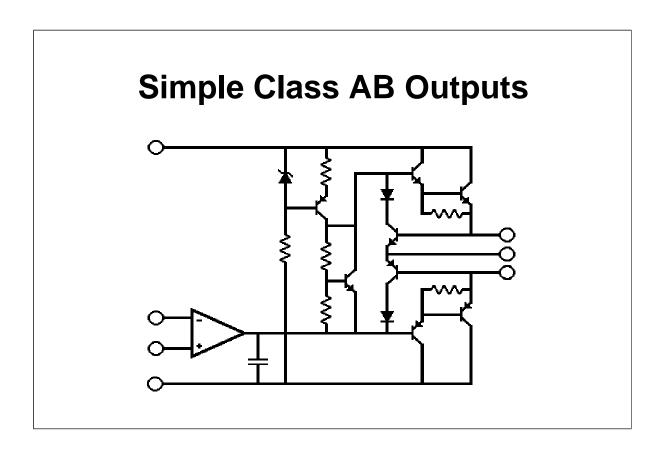

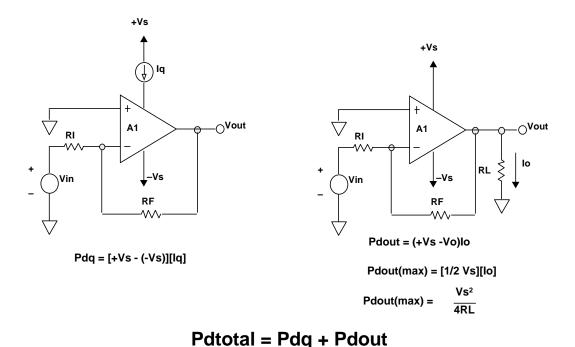

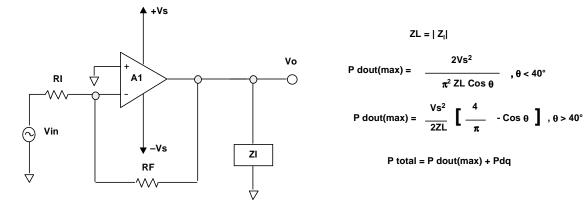

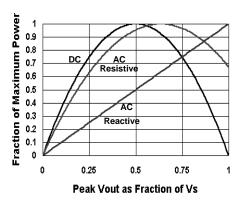

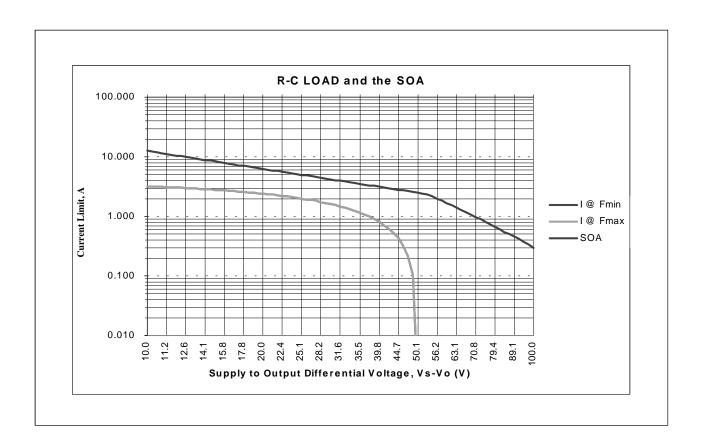

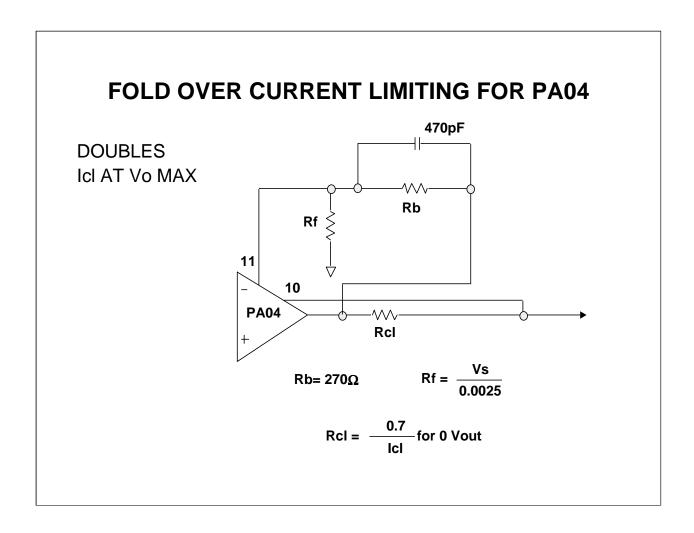

Class "C" output stages tie the bases or gates of the power devices together. Omitting the usual bias network between these bases reduces cost with the penalty of increased crossover distortion.