# Switchmode Lead-Acid Battery Charger

## **FEATURES**

- Accurate and Efficient Control of Battery Charging

- Average Current Mode Control from Trickle to Overcharge

- Resistor Programmable Charge Currents

- Thermistor Interface Tracks Battery Requirements Over Temperature

- Output Status Bits Report on Four Internal Charge States

- Undervoltage Lockout Monitors VCC and VREF

#### **DESCRIPTION**

The UC3909 family of Switchmode Lead-Acid Battery Chargers accurately controls lead acid battery charging with a highly efficient average current mode control loop. This chip combines charge state logic with average current PWM control circuitry. Charge state logic commands current or voltage control depending on the charge state. The chip includes undervoltage lockout circuitry to insure sufficient supply voltage is present before output switching starts. Additional circuit blocks include a differential current sense amplifier, a 1.5% voltage reference, a -3.9mV/°C thermistor linearization circuit, voltage and current error amplifiers, a PWM oscillator, a PWM comparator, a PWM latch, charge state decode bits, and a 100mA open collector output driver.

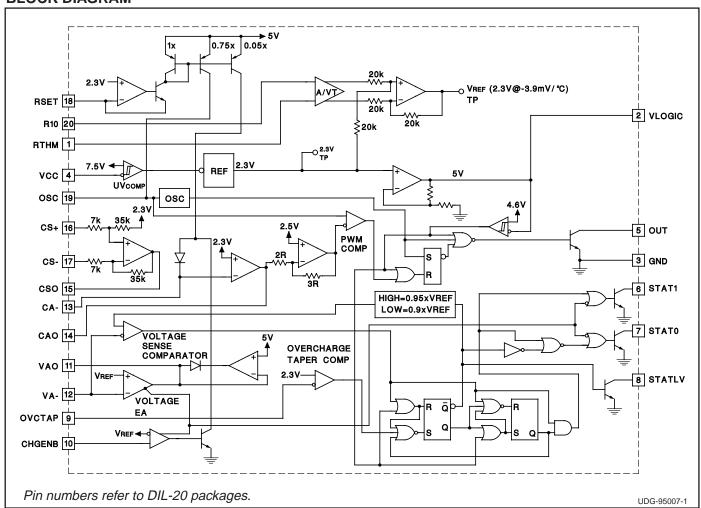

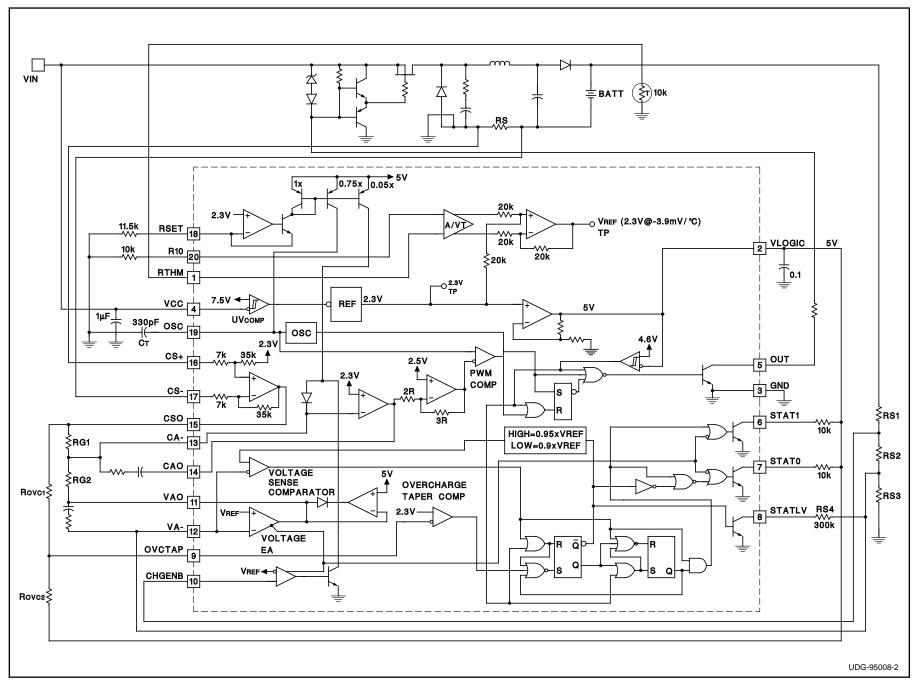

#### **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (VCC), OUT, STAT0, STAT                                | 140V                    |

|-----------------------------------------------------------------------|-------------------------|

| Output Current Sink                                                   |                         |

| CS+, CS                                                               | 0.4 to VCC (Note 1)     |

| Remaining Pin Voltages                                                | –0.3V to 9V             |

| Storage Temperature                                                   | –65°C to +150°C         |

| Junction Temperature                                                  | –55°C to +150°C         |

| Lead Temperature (Soldering, 10 sec.)                                 | +300°C                  |

| All currents are positive into, negative out of                       |                         |

| Consult Packaging Section of Databook for considerations of packages. | thermal limitations and |

|                                                                       |                         |

Note 1: Voltages more negative than -0.4V can be tolerated if current is limited to 50mA.

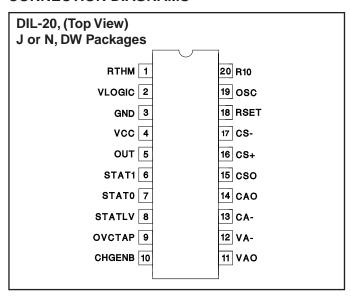

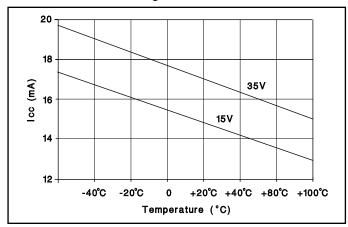

#### **CONNECTION DIAGRAMS**

**ELECTRICAL CHARACTERISTICS** Unless otherwise stated these specifications apply for  $TA = -40^{\circ}C$  to  $+85^{\circ}C$  for UC2909;  $0^{\circ}C$  to  $+70^{\circ}C$  for UC3909; CT = 330pF, RSET = 11.5k, R10 = 10k, RTHM = 10k, VCC = 15V, Output no load, RSTAT0 = RSTAT1 = 10k, CHGENB = OVCTAP = VLOGIC, TA = TJ.

| X UNITS   |

|-----------|

| <b>-</b>  |

| 0 V/V     |

| 0 V/V     |

| 5 mV      |

| dB        |

| dB        |

| 6 V       |

| 2 V       |

| 5 mA      |

| mA        |

| kHz       |

|           |

| β μΑ      |

| ) mV      |

| dB        |

| MHz       |

| 6 V       |

| V         |

| ).8<br>10 |

**ELECTRICAL CHARACTERISTICS (cont.)** Unless otherwise stated these specifications apply for  $TA = -40^{\circ}C$  to  $+85^{\circ}C$  for UC2909; 0°C to  $+70^{\circ}C$  for UC3909; CT = 330pF, RSET = 11.5k, R10 = 10k, RTHM = 10k, VCC = 15V, Output no load, RSTAT0 = RSTAT1 = 10k, CHGENB = OVCTAP = VLOGIC, TA = TJ.

| PARAMETER                                 | TEST CONDITION                                                               | MIN    | TYP   | MAX    | UNITS    |

|-------------------------------------------|------------------------------------------------------------------------------|--------|-------|--------|----------|

| Current Error Amplifier (CEA) Section     | (cont.)                                                                      |        |       |        |          |

| Output Source Current                     | CAO = 4V                                                                     |        | -25   | -12    | mA       |

| Output Sink Current                       | CAO=1V                                                                       | 2      | 3     |        | μΑ       |

| Ica-, Itrck_control                       | VCHGENB = GND                                                                | 8.5    | 10    | 11.5   | μΑ       |

| Voltage Error Amplifier (VEA) Section     |                                                                              |        |       |        |          |

| Ів                                        | Total Bias Current; Regulating Level                                         |        | 0.1   | 1      | μΑ       |

| Vio (VAO – Vref) (Note 2)                 | 8.8V < VCC < 35V, VCM = 2.3V, VAO = VA-                                      |        | 1.2   |        | mV       |

| Avo                                       | 1V < CAO < 4V                                                                | 60     | 90    |        | dB       |

| GBW                                       | $T_J = 25^{\circ}C, F = 100kHz$                                              | 0.250  | 0.500 |        | MHz      |

| Vol                                       | $Io = 500\mu A$                                                              |        | 0.4   | 0.6    | V        |

| Voн                                       | $IO = -500\mu A$                                                             | 4.75   | 5     | 5.25   | V        |

| Output Source Current                     | VAO = 4V                                                                     | -2     | -1    |        | mA       |

| Output Sink Current                       | VAO = 1V                                                                     | 2      | 2.5   |        | mA       |

| VAO Leakage: High Impedance State         | VCHGENB = GND, STAT0 = 0 & STAT1 = 0, VAO = 2.3V                             | -1     |       | 1      | μΑ       |

| Pulse Width Modulator Section             |                                                                              |        |       | '      |          |

| Maximum Duty Cycle                        | CAO = 0.6V                                                                   | 90     | 95    | 100    | %        |

| Modulator Gain                            | CAO = 2.5V, 3.2V                                                             | 63     | 71    | 80     | %/V      |

| OSC Peak                                  |                                                                              |        | 3     |        | V        |

| OSC Valley                                |                                                                              |        | 1     |        | V        |

| Oscillator Section (OSC)                  |                                                                              |        |       |        | '        |

| Frequency                                 | 8.8V < VCC < 35V                                                             | 198    | 220   | 242    | kHz      |

| Thermistor Derived Reference Section      | VID = VRTHM - VR10                                                           |        |       |        |          |

| Initial Accuracy, VAO (RTHM = 10k)        | VID = 0, R10 = RTHM =10k (Note 3)                                            | 2.2655 | 2.3   | 2.3345 | V        |

|                                           | $VID = 0$ , $R10 = RTHM = 10k$ , $-40^{\circ}C \le TA < 0^{\circ}C$ (Note 3) | 2.254  | 2.3   | 2.346  | V        |

| Line Regulation                           | VCC = 8.8V to 35V                                                            |        | 3     | 10     | mV       |

| VAO                                       | RTHM = 138k, R10 = 10k                                                       | 2.458  | 2.495 | 2.532  | V        |

|                                           | RTHM = 138k, R10 = 10k, -40°C ≤ TA < 0°C                                     | 2.445  | 2.495 | 2.545  | V        |

|                                           | RTHM = 33.63k, R10 = 10k                                                     | 2.362  | 2.398 | 2.434  | V        |

|                                           | RTHM = 33.63k, R10 = 10k, -40°C ≤ Ta < 0°C                                   | 2.350  | 2.398 | 2.446  | V        |

|                                           | RTHM = 1.014k, R10 = 10k                                                     | 2.035  | 2.066 | 2.097  | V        |

|                                           | RTHM = 1.014k, R10 = 10k, -40°C ≤ TA < 0°C                                   | 2.025  | 2.066 | 2.107  | V        |

| Charge Enable Comparator Section (C       | ,                                                                            |        | ı     |        | <b>'</b> |

| Threshold Voltage                         | As a function of VA-                                                         | 0.99   | 1     | 1.01   | V/V      |

| Input Bias Current                        | CHGENB = 2.3V                                                                | -0.5   | -0.1  |        | μΑ       |

| Voltage Sense Comparator Section (VS      | SC)                                                                          |        |       |        | •        |

| Threshold Voltage                         | STAT0 = 0, STAT1 = 0, Function of VREF                                       | 0.945  | 0.95  | 0.955  | V/V      |

|                                           | STAT0 = 1, STAT1 = 0, Function of VREF                                       | 0.895  | 0.9   | 0.905  | V/V      |

| Over Charge Taper Current Comparato       | r Section (OCTIC)                                                            | •      | II.   | ,      | •        |

| Threshold Voltage                         | Function of 2.3V REF, CA- = CAO                                              | 0.99   | 1     | 1.01   | V/V      |

| Input Bias Current                        | OVCTAP = 2.3V                                                                | -0.5   | -0.1  |        | μΑ       |

| Logic 5V Reference Section (VLOGIC)       |                                                                              |        |       |        |          |

| VLOGIC                                    | VCC = 15V                                                                    | 4.875  | 5.0   | 5.125  | V        |

| Line Regulation                           | 8.8V < VCC < 35V                                                             |        | 3     | 15     | mV       |

| Load Regulation                           | 0 < lo < 10mA                                                                |        | 3     | 15     | mV       |

| Reference Comparator Turn-on<br>Threshold |                                                                              |        | 4.3   | 4.8    | V        |

| Short Circuit Current                     | VREF = 0V                                                                    | 30     | 50    | 80     | mA       |

|                                           | ···=· • ·                                                                    |        |       |        |          |

**ELECTRICAL CHARACTERISTICS (cont.)** Unless otherwise stated these specifications apply for Ta = -40°C to +85°C for UC2909; 0°C to +70°C for UC3909; CT = 330pF, RSET = 11.5k, R10 = 10k, RTHM = 10k, VCC = 15V, Output no load, RSTAT0 = RSTAT1 = 10k, CHGENB = OVCTAP = VLOGIC, Ta = TJ.

| PARAMETER                       | TEST CONDITION                                  | MIN | TYP | MAX  | UNITS |

|---------------------------------|-------------------------------------------------|-----|-----|------|-------|

| Output Stage Section            |                                                 |     | •   | •    |       |

| ISINK Continuous                |                                                 |     | 50  |      | mA    |

| <b>I</b> PEAK                   |                                                 |     | 100 |      | mA    |

| Vol                             | Io = 50mA                                       |     | 1   | 1.3  | V     |

| Leakage Current                 | Vout = 35V                                      |     |     | 25   | μΑ    |

| STAT0 & STAT1 Open Collector Ou | utputs Section                                  | •   |     |      | _     |

| Maximum Sink Current            | Vout = 8.8V                                     | 6   | 10  |      | mA    |

| Saturation Voltage              | IOUT = 5mA                                      |     | 0.1 | 0.45 | V     |

| Leakage Current                 | Vout = 35V                                      |     |     | 25   | μΑ    |

| STATLV Open Collector Outputs   | Section                                         |     |     |      |       |

| Maximum Sink Current            | Vout = 5V                                       | 2.5 | 5   |      | mA    |

| Saturation Voltage              | IOUT = 2mA                                      |     | 0.1 | 0.45 | V     |

| Leakage current                 | VOUT = 5V                                       |     |     | 3    | μΑ    |

| UVLO Section                    |                                                 |     |     |      |       |

| Turn-on Threshold               |                                                 | 6.8 | 7.8 | 8.8  | V     |

| Hysteresis                      |                                                 | 100 | 300 | 500  | mV    |

| Icc Section                     |                                                 |     |     |      |       |

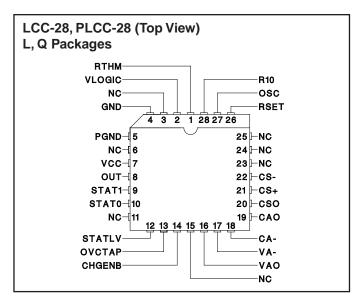

| Icc (run)                       | See Graph, typical temperature variation of ICC |     | 13  | 19   | mA    |

| Icc (off)                       | VCC = 6.5V                                      |     | 2   |      | mA    |

Note 2: VIO is measured prior to packaging with internal probe pad.

Note 3: Thermistor initial accuracy is measured and trimmed with respect to VAO; VAO = VA-.

#### **PIN DESCRIPTIONS**

**CA-:** The inverting input to the current error amplifier.

**CAO:** The output of the current error amplifier which is internally clamped to approximately 4V. It is internally connected to the inverting input of the PWM comparator.

**CS-, CS+:** The inverting and non-inverting inputs to the current sense amplifier. This amplifier has a fixed gain of five and a common-mode voltage range of from -250mV to +VCC.

**CSO:** The output of the current sense amplifier which is internally clamped to approximately 5.7V.

**CHGENB:** The input to a comparator that detects when battery voltage is low and places the charger in a trickle charge state. The charge enable comparator makes the output of the voltage error amplifier a high impedance while forcing a fixed  $10\mu A$  into CA- to set the trickle charge current.

**GND:** The reference point for the internal reference, all thresholds, and the return for the remainder of the device. The output sink transistor is wired directly to this pin.

**OVCTAP:** The overcharge current taper pin detects when the output current has tapered to the float threshold in the overcharge state.

**OSC:** The oscillator ramp pin which has a capacitor (CT) to ground. The ramp oscillates between approximately 1.0V to 3.0V and the frequency is approximated by:

frequency ≈

$$\frac{1}{1.2 \bullet \text{CT} \bullet \text{RSET}}$$

**OUT:** The output of the PWM driver which consists of an open collector output transistor with 100mA sink capability.

**R10:** Input used to establish a differential voltage corresponding to the temperature of the thermistor. Connect a 10k resistor to ground from this point.

**RSET:** A resistor to ground programs the oscillator charge current and the trickle control current for the oscillator ramp.

The oscillator charge current is approximately

The trickle control current (ITRCK\_CONTROL) is approximately

**RTHM:** A 10k thermistor is connected to ground and is thermally connected to the battery. The resistance will vary exponentially over temperature and its change is used to vary the internal 2.3V reference by -3.9mV/°C. The recommended thermistor for this function is part number L1005-5744-103-D1, Keystone Carbon Company, St. Marys, PA.

**STAT0:** This open collector pin is the first decode bit used to decode the charge states.

**STAT1:** This open collector pin is the second decode bit used to decode the charge states.

Figure 1. Icc vs. Temperature

**STATLV:** This bit is high when the charger is in the float state.

**VA-:** The inverting input to the voltage error amplifier.

**VAO:** The output of the voltage error amplifier. The upper output clamp voltage of this amplifier is 5V.

VCC: The input voltage to the chip. The chip is operational between 7.5V and 40V and should be bypassed with a  $1\mu F$  capacitor. A typical Icc vs. temperature is shown in Figure 1.

**VLOGIC:** The precision reference voltage. It should be bypassed with a  $0.1\mu F$  capacitor.

# **Charge State Decode Chart:**

STAT0 and STAT1 are open collector outputs. The output is approximately 0.2V for a logic 0.

|                | STAT1 | STAT0 |

|----------------|-------|-------|

| Trickle Charge | 0     | 0     |

| Bulk Charge    | 0     | 1     |

| Over Charge    | 1     | 0     |

| Float Charge   | 1     | 1     |

#### **APPLICATION INFORMATION**

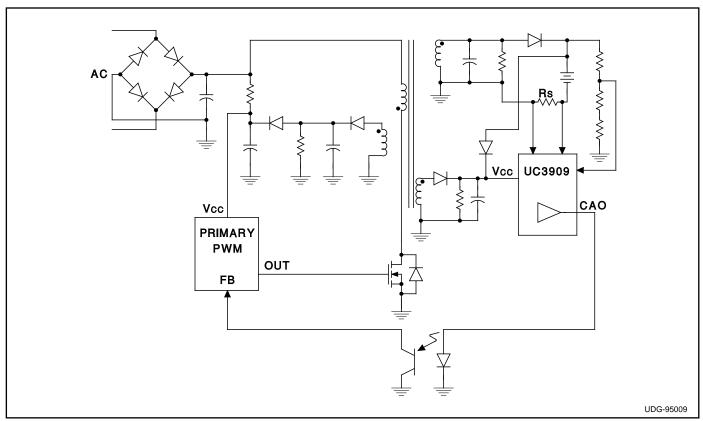

A Block Diagram of the UC3909 is shown on the first page, while a Typical Application Circuit is shown in Figure 2. The circuit in Figure 2 requires a DC input voltage between 12V and 40V.

The UC3909 uses a voltage control loop with average current limiting to precisely control the charge rate of a lead-acid battery. The small increase in complexity of average current limiting is offset by the relative simplicity of the control loop design.

## **CONTROL LOOP:**

## **Current Sense Amplifier:**

This amplifier measures the voltage across the sense resistor RS with a fixed gain of five and an offset voltage of 2.3V. This voltage is proportional to the battery current. The most positive voltage end of RS is connected to CS- ensuring the correct polarity going into the PWM comparator.

CSO = 2.3V when there is zero battery current.

RS is chosen by dividing 350mV by the maximum allowable load current. A smaller value for RS can be chosen

to reduce power dissipation.

Maximum Charge Current, IBULK, is set by knowing the maximum voltage error amplifier output, VOH = 5V, the maximum allowable drop across RS, and setting the resistors RG1 and RG2 such that:

(1)

$$\frac{\text{RG1}}{\text{RG2}} = \frac{5 \cdot \text{VRS}}{\text{VLOGIC} - \text{CA}} = \frac{5 \cdot \text{VRS}}{5\text{V} - 2.3\text{V}}$$

$$= \frac{5 \cdot \text{VRS}}{2.7\text{V}} = 1.852 \cdot \text{IBULK} \cdot \text{RS}$$

The maximum allowable drop across RS is specified to limit the maximum swing at CSO to approximately 2.0V to keep the CSO amplifier output from saturating.

No charge/load current: Vcso = 2.3V,

Max charge/load current: VMAX(CSO) = 2.3V - 2.0V = 0.3V

## **Voltage Error Amplifier:**

The voltage error amplifier (VEA) senses the battery voltage and compares it to the 2.3V – 3.9mV/°C thermistor generated reference. Its output becomes the current

**Figure 2. Typical Application Circuit**

command signal and is summed with the current sense amplifier output. A 5.0V voltage error amplifier upper clamp limits maximum load current. During the trickle charge state, the voltage amplifier output is opened (high impedance output) by the charge enable comparator. A trickle bias current is summed into the CA- input which sets the maximum trickle charge current.

The VEA, VOH = 5V clamp saturates the voltage loop and consequently limits the charge current as stated in Equation 1.

During the trickle bias state the maximum allowable charge current (ITC) is similarly determined:

(2) ITC =

$$\frac{ITRCK\_CONTROL \bullet RG1}{RS \bullet 5}$$

ITRCK\_CONTROL is the fixed control current into CA-. ITRCK\_CONTROL is  $10\mu A$  when RSET = 11.5k. See RSET pin description for equation.

## **Current Error Amplifier:**

The current error amplifier (CA) compares the output of the current sense amplifier to the output of the voltage error amplifier. The output of the CA forces a PWM duty cycle which results in the correct average battery current. With integral compensation, the CA will have a very high DC current gain, resulting in effectively no average DC current error. For stability purposes, the high frequency gain of the CA must be designed such that the magnitude of the down slope of the CA output signal is less than or equal to the magnitude of the up slope of the PWM ramp.

## **CHARGE ALGORITHM**

Refer to Figure 3 in UC3906 Data Sheet in the data book.

# A) Trickle Charge State STAT0 = STAT1 = STATLV = logic 0

When CHGNB is less than VREF ( $2.3V - 3.9mV/^{\circ}C$ ), STATLV is forced low. This decreases the sense voltage divider ratio, forcing the battery to overcharge (VOC).

(3)

$$VOC = (VREF) \frac{(RS1 + RS2 + RS3 || RS4)}{(RS3 || RS4)}$$

During the trickle charge state, the output of the voltage error amplifier is high impedance. The trickle control current is directed into the CA- pin setting the maximum trickle charge current. The trickle charge current is defined in Equation 2.

# B) Bulk Charge State STAT1 = STATLV = logic 0, STAT0 = logic 1

As the battery charges, the UC3909 will transition from trickle to bulk charge when CHGENB becomes greater than 2.3V. The transition equation is

$$VT = VREF \bullet \frac{(RS1 + RS2 + RS3 || RS4)}{(RS2 + RS3 || RS4)}$$

STATLV is still driven low.

During the bulk charge state, the voltage error amplifier is now operational and is commanding maximum charge current (IBULK) set by Equation 1. The voltage loop attempts to force the battery to VOC.

# C) Overcharge State STAT0 = STATLV = logic 0, STAT1 = logic 1

The battery voltage surpasses 95% of VOC indicating the UC3909 is in its overcharge state.

During the overcharge charge state, the voltage loop becomes stable and the charge current begins to taper off. As the charge current tapers off, the voltage at CSO increases toward its null point of 2.3V. The center connection of the two resistors between CSO and VLOGIC sets the overcurrent taper threshold (OVCTAP). Knowing the desired overcharge terminate current (loct), the resistors Rovc1 and Rovc2 can be calculated by choosing a value of Rovc2 and using the following equation:

# D) Float State STAT0 = STAT1 = STATLV = logic 1

The battery charge current tapers below its OVCTAP threshold, and forces STATLV high increasing the voltage sense divider ratio. The voltage loop now forces the battery charger to regulate at its float state voltage (VF).

(5)

$$V_F = (V_{REF}) \frac{(RS1 + RS2 + RS3)}{RS3}$$

If the load drains the battery to less than 90% of VF, the charger goes back to the bulk charge state, STATE 1.

#### **OFF LINE APPLICATIONS**

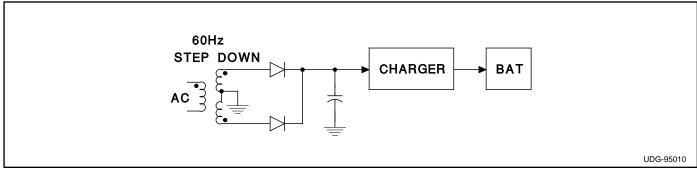

For off line charge applications, either Figure 3 or Figure 4 can be used as a baseline. Figure 3 has the advantage of high frequency operation resulting in a small isolation transformer. Figure 4 is a simpler design, but at the expense of larger magnetics.

Figure 3. Off Line Charger with Primary Side PWM

Figure 4. Isolated Off Line Charger